### **ORIGINAL RESEARCH**

# Synthesis of Parallel Software from Heterogeneous Dataflow Models

Omair Rafique<sup>1</sup> · Klaus Schneider<sup>1</sup>

Received: 2 October 2021 / Accepted: 21 March 2022 / Published online: 26 April 2022 © The Author(s) 2022

### Abstract

Dataflow process networks (DPNs) are intrinsically data-driven, i.e., node actions are not synchronized among each other and may fire whenever sufficient input operands arrived at a node. While the general model of computation (MoC) of DPNs does not impose further restrictions, many different subclasses of DPNs representing different dataflow MoCs have been considered over time. These classes mainly differ in the kinds of behaviors of the processes. A DPN may be heterogeneous in that different processes in the network belong to different classes of DPNs. A heterogeneous DPN can therefore be effectively used to model and to implement different components of a system with different kinds of processes and, therefore, different dataflow MoCs. This paper presents a model-based design based on different dataflow MoCs including their heterogeneous combinations. In particular, it covers the automatic software synthesis of systems from DPN models. The main objective is to validate, evaluate and compare the artifacts exhibited by different dataflow MoCs at the implementation level of systems under the supervision of a common design tool. Moreover, this work also offers an efficient synthesis method that targets and exploits heterogeneity in DPNs by generating implementations based on the kinds of behaviors of the processes. The proposed synthesis method provides a tool chain including different specialized code generators for specific dataflow MoCs, and a runtime system that finally maps models using a combination of different dataflow MoCs on cross-vendor target hardware.

Keywords Dataflow process networks · Heterogeneity · Automatic synthesis

# Introduction

### The State of the Art

In a model-based design of embedded systems, we start by focusing on models that describe the functional behavior of the system. These models are hardware independent and are based on a particular model of computation (MoC). A MoC determines *why, when, which atomic action of a system is executed*. A model-based design is typically equipped with a tool chain that following a correctness-by-construction approach finally produces executable code. The code can

This article is part of the topical collection "Model-Driven Engineering and Software Development" guest edited by Slimane Hammoudi and Luis Ferreira Pires.

Omair Rafique rafique@cs.uni-kl.de

> Klaus Schneider schneider@cs.uni-kl.de

<sup>1</sup> Department of Computer Science, University of Kaiserslautern, Kaiserslautern, Germany then be deployed on the target hardware such as a CPU, a GPU or even an FPGA depending on the target application. Depending on the application as well as on the target architecture, different MoCs have their own advantages and disadvantages.

For example, when it comes to real-time systems, the synchronous reactive (SR) [5, 6, 43] MoC greatly simplifies many efforts in the validation and verification. In fact, it has proven its usefulness both on single-core and multi-core platforms, as well as on application-specific hardware platforms in safety critical applications such as avionics [12] and other embedded system industries. However, when it comes to soft real-time applications such as streaming and signal processing [28], performance and design flexibility are often dominant factors over safety, and commercial off-the-shelf (COTS) heterogeneous hardware platforms are preferred [2]. The generation of distributed implementations is often desired for such applications where different components are mapped and executed on different computing units (devices). For such applications, especially when implemented on heterogeneous platforms, synchronization and communication

overheads caused by synchronous semantics often reduce the performance [1].

Instead, asynchronous models or dataflow process networks (DPNs) [11, 22, 23] are well-suited for the implementation of such systems. In particular, they explicitly expose the concurrency of applications and thereby simplify their execution on parallel and heterogeneous architectures. However, it is not beneficial to start with DPNs in model-based designs since DPNs do not lend themselves well for simulation and verification. In particular, major correctness properties like buffer boundedness and absence of deadlocks are not decidable for general DPNs [18, 29]. Therefore, both SR and DPNs have their own advantages and disadvantages.

As an alternative, *desynchronization* of synchronous models [4, 19] has been developed that benefits both from the static analysis methods for synchronous systems and the performance of the finally synthesized asynchronous systems. Desynchronization techniques [1, 4, 31] are used to convert synchronous models into asynchronous ones to more efficiently support distributed implementations. These techniques preserve the functional specification of the synchronous models and, moreover, preserve properties like deadlock-freedom and bounded memory usage that are otherwise difficult to ensure in DPNs. These desynchronized models [1, 3] are the *starting point* of this work. The resulting dataflow models are free from deadlocks and even buffers with only single entries are sufficient for a successful execution.

### **Motivation and Problem Setting**

DPNs consist of statically defined process nodes with firstin-first-out (FIFO) buffered point-to-point connections. The process nodes are not synchronized among each other and may fire whenever sufficient data is available for a node. While the general MoC of DPNs does not impose further restrictions, many different classes of DPNs have been considered over time like Kahn process networks (KPN) [22], (cyclo-)static dataflow (SDF) [30] networks and Boolean dataflow (BDF) [10] networks. Each class defines a specific dataflow MoC by specifying a particular execution and communication semantics [16]. These classes mainly differ in the kinds of behaviors of the processes which affect on the one hand the expressiveness of the DPN class as well as the methods for their analysis (predictability) and synthesis (efficiency). These behaviors are precisely described based on the underlying semantics of how each process is triggered for an execution, and how each execution of a process consumes/produces data. A process in a static DPN exhibits a static behavior where a statically determined amount of data is consumed and produced in each execution. Second, a process in a KPN has a sequential behavior where a dynamically determined amount of data is consumed and produced sequentially in each execution. In contrast, a

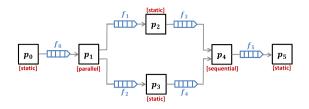

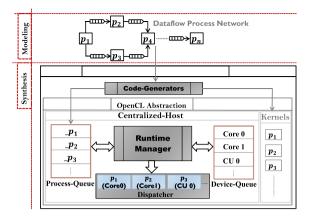

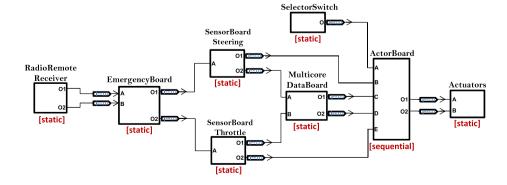

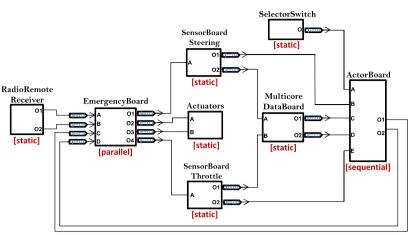

**Fig. 1** A simple visualization of a heterogeneous DPN. It consists of different kinds of processes  $(p_0, \ldots, p_5)$  characterized by static, sequential and parallel behaviors. The processes  $(p_0 \ldots, p_5)$  are connected together via FIFO buffered point-to-point channels  $(f_0, \ldots, f_5)$

process in a dynamic dataflow (DDF) network may have a parallel behavior that can consume and produce a dynamically determined amount of data in parallel. A DPN may be heterogeneous in that different processes in the network may belong to different classes of DPNs. A heterogeneous combination of particular kinds of processes can be used to model and implement different components of a system with different kinds of processes and, therefore, different dataflow MoCs. A simple example of a heterogeneous DPN consisting of different kinds of behaviors of the processes is visualized in Fig. 1.

Design tools for modeling [9, 14, 20, 24, 42, 49] are used to model and to design parallel embedded systems using certain MoCs, including different dataflow MoCs. However, there is a lack of automatic synthesis methods to analyze and to evaluate the artifacts exhibited by particular MoCs. Second, the existing design tools for synthesis like [8, 28, 45] are usually restricted to the weakest classes of DPNs, i.e., to cyclo-static and static DPNs where each tool only supports a specific dataflow MoC. For heterogeneous DPNs offering heterogeneous combinations of different kinds of behaviors of the processes, the synthesis method should exploit this heterogeneity by generating efficient implementations based on the dataflow MoC of each process.

Apart from efficiency, another crucial challenge is the portability of applications on different cross-vendor platforms which is not systematically handled by the traditional design flows. In general, a non-trivial manual effort is finally required for deploying automatically generated code to a particular target architecture.

The overall motivation of this work is to enable the automatic software synthesis of systems using different dataflow MoCs including their heterogeneous combinations. The main objective is to validate, evaluate and compare the artifacts exhibited by different dataflow MoCs at the implementation level of systems under the supervision of a common design tool. Moreover, the idea is to offer an efficient synthesis method that exploits heterogeneity in dataflow networks by generating implementations based on the kinds of behaviors of the processes. Finally, this work also considers the challenge of systematically handling the portability of modeled systems on cross-vendor heterogeneous platforms as an integral part of the synthesis process.

### Contributions

We propose a synthesis design flow that essentially enables the automatic software synthesis of systems based on different dataflow MoCs. In particular, it supports three different dataflow MoCs, namely synchronous (static) dataflow (SDF) [26], Kahn process networks (KPN) [21], and a deterministic variant of dynamic dataflow (DDF). The common design tool can be effectively used to generate implementations based on the individual dataflow MoCs [32, 35, 41]. Moreover, in contrast to existing dataflow oriented synthesis methods, the proposed method efficiently targets and exploits heterogeneity in dataflow networks by generating implementations purely based on the kinds of behaviors of the processes or the underlying dataflow MoC of each process [36].

The target DPN model of our desynchronization method is based on a limited subset of the Cal actor language (CAL) [13]. The proposed synthesis design flow provides a comprehensive tool chain, including different specialized code generators for specific dataflow MoCs, and a runtime system that finally maps models using a combination of different dataflow MoCs on the target hardware. The tool chain essentially offers a platform-independent code synthesis method based on the open computing language (OpenCL) [47] abstraction that enables a more generalized synthesis targeting COTS heterogeneous architectures. In particular, this work focuses on mapping modeled systems on crossvendor multi-core CPUs and many-core GPUs.

The main contributions of this work can be summarized as follows:

- We propose an automatic model-based synthesis that allows us to synthesize systems using different dataflow MoCs, namely the SDF MoC, the KPN MoC and a deterministic variant of the DDF MoC.

- We implemented a platform-independent code synthesis method for CAL DPN models. In particular, we offer a synthesis tool chain that automatically synthesizes CAL models into platform-independent OpenCL code.

- We offer a single back-end based on OpenCL which is comprised of different specialized code generators for specific dataflow MoCs.

- We present the runtime system designed under the OpenCL abstraction for finally deploying DPNs on cross-vendor COTS target hardware.

### **Related Work**

A number of model-based design tools have been presented over time for the design and development of embedded systems. This section covers a number of well-established design tools, categorized mainly from the perspective of desired goals, employed strategies and usage as given in the following sections.

### **Design Tools for Modeling**

The Ptolemy project [9, 14] is a design tool originally constructed in a Java-based environment to support the modeling and simulation of behaviors based on different MoCs, including particular dataflow MoCs. Although the main focus is to study and analyse different MoCs at the modeling level, it also provides preliminary code generators.<sup>1</sup> It requires a supporting helper code for each process which is provided manually using a fairly complex procedure. FERAL [24] is another framework developed to provide a holistic model-based design approach to enable the coupling of specialized simulators in offline scenarios, i.e., without connecting them to real hardware. This project very interestingly adopts and extends the concepts from the Ptolemy project.

The formal system design (ForSyDe) [42] tool offers a formal design methodology for embedded systems based on different MoCs including the SR MoC and two particular dataflow MoCs. Although the major focus of this design tool is the modeling framework, it also provides a hardware synthesis tool that has been mainly elaborated for translating models limited to the SR MoC into the corresponding VHDL code. Another synthesis plug-in called  $f2cc^2$  has been introduced for generating GPGPU software code from models limited to the SR MoC.

The SystemC models of computation (SysteMoC) [20] is an actor-oriented dataflow programming language built on top of SystemC. Besides supporting different dataflow MoCs, it also offers the automatic MoC identification of processes (actors), which is not featured in frameworks like Ptolemy and ForSyDe. Although the main focus of SysteMoC has been at the design level, the System-CoDe-signer [20] framework specializes in automatic design space exploration starting from SysteMoC models. In particular, the framework offers a platform-based automatic system generation from SysteMoC models.

SDF for free  $(SDF^3)$  [49] is a versatile experimental tool that can generate random static dataflow graphs (SDFGs)

<sup>&</sup>lt;sup>1</sup> http://ptolemy.berkeley.edu/ptolemyII/ptII10.0/ptII10.0.1/ptolemy/ cg/.

<sup>&</sup>lt;sup>2</sup> https://github.com/forsyde/f2cc/wiki.

with support to analyse and visualize these graphs. It supports three different classes of static DPNs, namely the static dataflow (SDF) [26], the cyclo-static dataflow (CSDF) [15] and the scenario-aware dataflow (SADF) [48]. The tool includes an extensive library of SDFG analysis and transformation algorithms as well as functionality to visualize and simulate them.

#### **Design Tools for Synthesis**

Model-based design tools for synthesis in the related stateof-the-art mainly differ by their employed MoCs. A number of dataflow-oriented design tools have been presented where each tool usually only supports a specific dataflow MoC. To this end, some of the inspiring model-based design tools for synthesis are presented in [8, 28, 44, 45] (to name a few).

The framework presented in [45] introduces a design flow for executing applications specified as SDF graphs on heterogeneous systems using OpenCL. However, it only supports the execution of behaviors limited to SDF.

The work presented in [28] translates DPNs modeled using a subset of CAL to parallel programs based on OpenCL. The methodology incorporates static analysis and transformations and thus confined to the synthesis of SDF models. Similarly, the dataflow oriented framework [8] proposes a dataflow MoC as a symmetric-rate dataflow, a variant of SDF where the token production rate and the token consumption rate per FIFO channel is symmetric.

The distributed application layer (DAL) framework [44] presents a scenario-based design flow for mapping streaming applications onto heterogeneous on-chip many-core systems. Behaviors are modeled based on a specific dataflow MoC, namely the KPN MoC [22], and the execution scenarios are coordinated using a finite state machine (FSM).

### **Design Tools Used in Industry**

One of the most popular and commercially recognized model-based design tool Matlab<sup>3</sup> has introduced a variety of supporting toolkits over time. Interestingly, Matlab Simulink introduced the dataflow domain<sup>4</sup> where applications can be modeled and simulated based on the SDF MoC. The main objective of introducing the dataflow domain is to improve the simulation throughput with multithreaded execution.

The Signal Processing Worksystem (SPW) from Cadence Design Systems<sup>5</sup> supports the modeling and analysis of signal processing algorithms based on static as well as dynamic dataflow models. The design flow mainly focuses on the

| Tools                 | Multiple<br>dataflow<br>MoCs | Automatic<br>synthesis | Heterogeneous<br>synthesis | Heterogeneous<br>target hardware |

|-----------------------|------------------------------|------------------------|----------------------------|----------------------------------|

| Ptolemy [9, 14]       | ✓                            | ×                      | ×                          | ×                                |

| SysteMoC [20]         | ✓                            | ✓                      | ×                          | ×                                |

| FERAL [24]            | ✓                            | ×                      | ×                          | ×                                |

| SDF <sup>3</sup> [48] | ✓                            | ×                      | ×                          | ×                                |

| Schor et al. [45]     | ×                            | ✓                      | ×                          | $\checkmark$                     |

| PRUNE [8]             | ×                            | ✓                      | ×                          | ✓                                |

| DAL [44]              | ×                            | ✓                      | ×                          | ×                                |

| Lund et al. [28]      | ×                            | ✓                      | ×                          | √                                |

| Proposed tool         | ✓                            | 1                      | ×                          | 1                                |

Fig. 2 Comparison of the proposed framework with related tools

simulation and manual refinement of modeled systems. Similarly, CoCentric System Studio from Synopsys<sup>6</sup> is a systemlevel design solution consisting of tools, methodologies, and libraries that enables the design and simulation of systemson-a-chip. The modeling paradigms can be hierarchically mixed at all levels for e.g., based on nested dataflow models and FSMs. The main emphasis of the design flow is the modeling and analysis of complex systems.

### Summary

In general, model-based design tools for embedded systems that support heterogeneous combinations of MoCs including different dataflow MoCs are of particular interest for modeling and analysis of complex systems. These frameworks, developed and evolved over decades, are used to formally analyse different MoCs for modeling and designing embedded systems. Some of the design tools in this category also introduced a synthesis facility, supporting platform-dependent synthesis methods usually restricted to implementations based on particular MoCs. In general, there is a lack of automatic synthesis methods to analyse and to evaluate different dataflow MoCs. Second, the existing design tools for synthesis are usually dedicated to automatically implementing systems based on a specific dataflow MoC. Therefore, a common synthesis design flow is still needed that mainly focuses and emphasizes on the automatic software synthesis of systems based on different dataflow MoCs. Moreover, an efficient software synthesis method is desired that targets and essentially exploits heterogeneity in dataflow networks by generating implementations based on the dataflow MoC of each process. The features offered by the proposed tool in comparison to related tools are summarized in Fig. 2.

<sup>&</sup>lt;sup>3</sup> http://www.mathworks.com/matlabcentral/.

<sup>&</sup>lt;sup>4</sup> https://www.mathworks.com/help/dsp/ug/dataflow-domains.html/.

<sup>&</sup>lt;sup>5</sup> https://www.cadence.com/.

<sup>&</sup>lt;sup>6</sup> https://www.synopsys.com/.

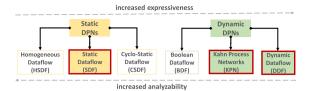

**Fig. 3** Categorization of various dataflow MoCs. Different dataflow MoCs are categorized into static and dynamic ones. The static DPNs are ones having fixed consumption and production rates. Whereas, the dynamic DPNs involve variable consumption and production rates. The analyzability of DPNs is inversely related to their expressiveness. The dataflow MoCs supported in this work are highlighted by colored boxes

### Preliminaries

This section highlights the background of this work by presenting some important preliminaries. This includes the tools and specifications used as essential parts of the proposed design flow.

### **Dataflow Process Networks**

A dataflow process network (DPN) [11, 22, 23] describes the behavior of a system by distributing it in a set of independent process nodes that interact with each other only through FIFO buffered point-to-point channels, as shown in Fig. 1. Each process performs a computation by firing where it consumes data tokens from its input buffers and produces data tokens for its output buffers. The behavior of each process is described by firing rules which are triggered by the availability of data. The general MoC of DPNs does not impose further restrictions. However, a number of different classes of DPNs representing different dataflow MoCs have been considered over time [16]. These classes mainly differ in the kinds of behaviors of the processes. These behaviors are precisely described based on the underlying semantics of how each atomic process is triggered for an execution, and how each execution of a process consumes/produces data, in particular, whether a statically or dynamically determined amount of data is consumed and produced. Based on that, the most commonly known classes can be categorized into static and dynamic DPNs as depicted in Fig. 3.

The latter accommodates DPNs like Kahn process networks (KPN) [22], Boolean dataflow (BDF) [10] and the dynamic dataflow (DDF) networks. Whereas, the former includes DPNs like static dataflow (SDF) [26, 30], homogeneous synchronous dataflow (HSDF) [26] and the cyclostatic dataflow (CSDF) [15] networks. Static DPNs are generally characterized as having only processes where the consumption and production of tokens are neither influenced by the values of the consumed tokens nor are they dependent on the points in time at which tokens arrive on the input buffers. Thus, processes in static DPNs always consume the same number of input tokens from particular input buffers and produce the same number of output tokens to particular output buffers. However, they may read different number of tokens from different input buffers and may write different number of tokens to different output buffers. On the one hand, these characteristics allow powerful design-time analysis techniques (e.g., for performance analysis and verification), but on the other hand, they limit the expressiveness by excluding dynamic behaviors (like select and switch nodes).

In contrast to static DPNs, processes in dynamic DPNs can vary the consumption and production of tokens in each firing dependent on the history of the consumed tokens and also on the tokens to be consumed. This allows conditional or data-dependent executions of processes; in particular, each process can produce and consume a different number of tokens in every firing. This generalization results in higher expressiveness and flexibility but makes the analysis more difficult.

In general, DPNs offer a modeling paradigm well suited for the modeling of concurrent embedded systems. However, model-based designs starting with dynamic DPNs have to deal with analyzability issues, i.e., the undecidability of checking major correctness properties like buffer boundedness and absence of deadlocks. Therefore, implementations of concurrent and distributed embedded systems from DPNs like KPNs may suffer from problems like deadlocks and buffer overflows [18, 29].

#### **Desynchronized DPN Model**

As a long-term project, our group developed the Averest<sup>7</sup> tool for a model-based design process starting with synchronous models. The Averest project aims at providing a complete set of tools for the development of reactive systems. Moreover, the work presented in [1, 3] further presents a desynchronization design flow based on Averest. The complete design flow based on Averest is presented in [2]. Since synchronous models are particularly well suited for analysis, the design flow starts with synchronous models, verifies them for desynchronization and then translates them to DPNs for the synthesis of concurrent and distributed systems. The underlying language of the target DPN model is a limited subset of CAL. Since, the proposed synthesis method targets the execution and deployment of DPNs on heterogeneous platforms consisting of different types of devices including GPUs, the desynchronization method generates stateless dataflow processes. This simplifies not only the target DPN specification for the final synthesis, but also paves the way for dynamically handling parallelization in OpenCL

<sup>&</sup>lt;sup>7</sup> http://www.averest.org.

Fig. 4 A simple example of a producer-consumer network

based synthesized implementations. Moreover, because of the great similarity between synchronous guarded actions (SGAs) as the *Averest* intermediate format (AIF) and CAL guarded actions, the correctness of the translation method is easily verified.

The target subset of CAL, therefore, simply consists of a set of guarded actions. Thereby, each generated stateless process essentially consists of a set of guarded actions where the guards are applied to the values of the input tokens. Depending on the behavior of a particular synchronous module, the generated process possesses a particular kind of behavior that precisely determines a particular dataflow MoC. To exemplify, CAL processes based on different supported dataflow MoCs are illustrated in Figs. 9, 10, and 11.

Apart from processes, the topology of the network is usually described using the functional network language (FNL) based on the XML format [7]. A simple producer-consumer dataflow network, as shown in Fig. 4, is specified in FNL as shown in Listing 1. This example shows the two most basic elements of FNL, namely the *Instance* and the *Connection*. Each *Instance* field defines a process instance (Lines 2–4 and 5–7), and possibly can even refer to another network. Each *Connection* field defines a connection between an input port and an output port of two instances (Lines 8–11).

Hence, the generated desynchronized CAL code consists of two parts: the CAL processes and the network description.

### **Open Computing Language**

The open computing language OpenCL [47] has been designed for parallel computing on cross-vendor and heterogeneous architectures. In contrast to proprietary specification languages with limited hardware choices, OpenCL allows task-parallel and data parallel heterogeneous computing on a heterogeneous collection of modern central processing units (CPUs), graphical processing units (GPUs), digital signal processors (DSPs), and other microprocessor designs organized into a single platform [25, 46].

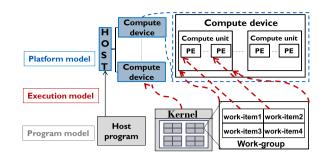

A primary benefit of OpenCL is a substantial acceleration in parallel processing. OpenCL supports both coarse-grained (task-level) as well as fine-grained (data-level) parallelism. Second, it provides the ability to write vendor-neutral cross platform applications. These benefits can be derived by understanding and exploiting a set of abstract models provided by OpenCL, as depicted in Figs. 5 and 6.

**Fig. 5** Overview of the OpenCL architecture: the *platform model* provides a standard abstraction of the target hardware. The *program model* specifies the behavior of a system typically organized as a host and several kernels. The *execution model* describes the mapping of the program model onto the platform model

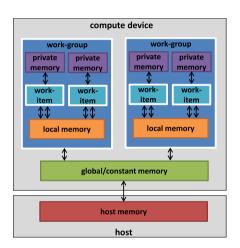

**Fig. 6** OpenCL memory model consists of five regions: The *host memory* is only accessible to the host processor. The *global memory* is accessible to both the host and device. The *constant memory* is fully accessible to the host and write-protected for the device. The *local memory* is only visible to the host and is local to a single compute unit. The *private memory* is private to an individual work-item executing within an OpenCL processing element https://www.khron os.org/registry/OpenCL/specs/2.2/html/OpenCL\_API.html

| 1 <  | XDF name="ConProd">                                                             |

|------|---------------------------------------------------------------------------------|

| 2    | <pre><instance id="producer"></instance></pre>                                  |

| 3    | < <b>Class</b> name="cal.producer"/>                                            |

| 4    |                                                                                 |

| 5    | <pre><instance id="consumer"></instance></pre>                                  |

| 6    | < <b>Class</b> name="cal.consumer"/>                                            |

| 7    |                                                                                 |

| 8    | <pre>Connection dst="consumer" dst-port="inp1"</pre>                            |

| 9    | <pre>src="producer" src-port="out1"/&gt;</pre>                                  |

| 10   | <pre><connection <="" dst="consumer" dst-port="inp2" pre=""></connection></pre> |

| 11   | <pre>src="producer" src-port="out2"/&gt;</pre>                                  |

| 12 < | /XDF>                                                                           |

**Listing 1** The FNL network description for the producer-consumer example as shown in Fig. 4.

### **Platform Model**

The OpenCL platform model provides users with a convenient abstraction of the target hardware. It is defined as a *host* connected to one or more compute devices, each having multiple compute units (CUs), each of which further consists of multiple processing elements (PEs).

A host is typically a CPU running a standard operating system (OS), while a compute device may be a GPU, a DSP, a further multicore CPU or any other specific microprocessor. Each device, therefore, consists of a collection of one or more CUs where each CU can be conceived as, for instance, a core of a CPU, or a streaming multiprocessor of a GPU. A CU is further composed of one or more PEs that execute instructions. Each PE can, therefore, be conceived as, for instance, a streaming core (or SIMD lane) of a GPU. An OpenCL device, therefore, executes the instruction computations on the PEs within the device.

### **Program Model**

The OpenCL program model is comprised of two main components: the *host program* and *kernels*. The host program executes on the host, defines device contexts, sets up command queues of devices and enqueues instances of kernel executions on devices.

**Kernels:** A kernel is a C-like function that actually implements the abstract behavior of the system or part of the system. OpenCL targets the parallel execution of a kernel on compute devices by organizing it into a computation domain. This computation domain is defined when a kernel is mapped for execution on the command queue. Each independent element of this domain represents the execution instance of the kernel and is termed as the *work-item*. Each work-item performs the same kernel function but on different data. OpenCL also allows grouping work-items together into *work-groups*, as shown in Fig. 5. All work-items in the same work-group are executed together on the same compute unit.

**Host Program:** It resides and executes on the host and is responsible for setting up and handling the execution of kernels on the compute devices using the defined context. The context essentially sets up the environment for executing kernels and is created with a set of devices. After the context is created, command queues are created where the kernels are mapped to get executed on the OpenCL devices associated with the context. Each command queue can represent a complete device (e.g., a CPU) or even a compute unit of that device (e.g., a CPU-core).

#### **Execution Model**

The OpenCL execution model can be understood as the mapping of kernels on the platform model which is implemented in the host program. Depending on the target compute device (e.g., a CPU or a GPU), kernels are mapped differently. In case of GPUs, OpenCL only allows the user to create a command queue at the level of a compute device. Hence, for a GPU, a kernel is typically allocated on a compute device, a work-group is ideally mapped on a CU, and work-items of that work-group are executed by PEs of that CU, as depicted in Fig. 5. In contrast, for CPUs, a command queue can be created at the level of a compute device as well as at the level of a CU. For the latter, the whole kernel (all work-groups) are mapped to the same CU (i.e., a core of a CPU).

### **Memory Model**

OpenCL offers a disjoint memory model to programmers as shown in Fig. 6. This is mainly because OpenCL targets heterogeneous platforms where most platforms utilize disjoint memory systems due to different memory requirements of different architectures. OpenCL visualizes its target as a system where data sharing between the host and compute devices is performed explicitly by a system network, such as a peripheral component interconnect (PCI) bus. The OpenCL memory model is organized in five regions consisting of *host*, *global*, *constant*, *local* and *private* memories. For heterogeneous architectures consisting of multiple devices integrated on a single platform, host memory and device memory are independent of one another. This requires the explicit handling of data from host memory to device memory and back to host.

### The Design Flow: Overview

The overall design flow can be understood in two parts, i.e., the modeling part and the synthesis part as shown in Fig. 7. In general, the starting point of this work is a desynchronized model. The desynchronization method based on our Averest tool finally generates a CAL DPN based on the supported dataflow MoCs. To this end, a general CAL DPN model is considered that relies on an abstract notion of a process. A process is composed of a finite set of actions where each action can perform a computation by consuming tokens from input buffers and producing tokens to output buffers. This general model is used with specific constraints and restrictions to specify the precise dataflow MoCs. Each supported dataflow MoC interprets the behavior of the CAL process in two parts: (i) process triggering or scheduling and (ii) process execution. The triggering behavior determines the conditions under which the dataflow MoC triggers a process

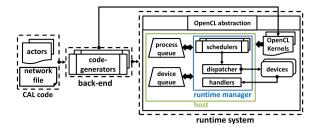

Fig. 7 The basic building block diagram [35] of the proposed framework. It can be understood in two phases: the modeling phase is in general provided with the desynchronized CAL DPN models. The synthesis phase employs the OpenCL abstraction and features a tool chain involving the specialized code generators and the runtime system that finally executes and maps the desynchronized models on the OpenCL abstracted target hardware

for an execution whereas the execution behavior determines how a process consumes/produces data when it is triggered for an execution. The framework supports three different dataflow MoCs, namely the synchronous (static) dataflow (SDF) [26] MoC, the Kahn process networks (KPN) [21] MoC and a deterministic variant of the dynamic dataflow (DDF) MoC. The general DPN model based on the used CAL subset and the supported dataflow MoCs are described in Sect. "Modeling: Dataflow Models". The desynchronized model consisting of CAL processes and the network specification is provided as input to the synthesis phase.

The synthesis part as shown in Fig. 7 provides a comprehensive tool chain, including a single back-end that offers different specialized code generators for different dataflow MoCs, and a runtime system which finally executes DPNs on the target hardware. Using OpenCL [47], it incorporates a standard hardware abstraction for cross-vendor heterogeneous hardware architectures. The proposed framework conceptually employs OpenCL as an operating system (OS) in the sense that it provides: common services for managing the target hardware, software resources and the implementation of modeled systems based on the supported dataflow MoCs. As discussed, OpenCL offers a programming model consisting of a host and several kernels where the host is a centralized entity that is connected to one or more computing devices and is responsible for the execution of kernels [33].

The framework adopts this idea of host and kernels for the synthesis as shown in Fig. 7. The synthesis method uses a combination of different code generators which generates an OpenCL kernel for each process in the network based on the underlying dataflow MoC of that process. In particular, the generated kernel implements the execution behavior of the

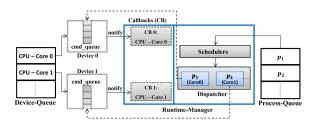

SN Computer Science

process. A single back-end based on OpenCL is developed that provides different specialized code generators for specific dataflow MoCs. Each code generator generates kernel code based on its underlying dataflow MoC. The runtime system systematically employs OpenCL as an integral part of the synthesis and manages the scheduling of processes and their communication based on the dataflow MoC of each process. A scheduler is designed for each dataflow MoC that schedules a process based on the triggering semantics of the underlying MoC. The runtime system is organized in a centralized host and kernels architecture under the OpenCL abstraction. The host accommodates different essential components along with the Runtime-Manager. The Runtime-Manager exploits other components of the host and provides different low-level implementations to finally execute the modeled DPNs (kernels) on the target hardware. The backend comprising of different code generators and the runtime system based on OpenCL are presented in Sect. "Synthesis: The Toolchain".

# **Modeling: Dataflow Models**

The target dataflow process network (DPN) model is based on a limited subset of CAL that is comprised of stateless processes having guarded actions. The main purpose of this section is not to present the formal specification of dataflow models of computation (MoCs) as this has been thoroughly considered in the literature [17, 18]. Instead, the main idea here is to informally illustrate how CAL is used to specify general DPNs and how this general model is restricted to specify different classes of dataflow MoCs. We, therefore, first present the syntax and the informal semantics of the general DPN model based on the used CAL subset and then illustrate the constraints to specify the supported dataflow MoCs.

### **The General Model of DPN**

Recall that a DPN is a set of processes  $\mathcal{P} = \{p_0, \dots, p_{m-1}\}$  with static point-to-point connections via FIFO buffers  $\mathcal{F} = \{f_0, \dots, f_{n-1}\}$ . We also assume a total order  $\leq$  on the FIFO buffers so that we can unambiguously switch from sets to tuples of FIFO buffers by simply ordering the corresponding set to a tuple. For this reason, we often ignore the difference between sets and the corresponding tuples. For any tuple  $t = (t_0, \dots, t_{\ell})$ , we denote its components as  $t_i = \text{proj}_i(t)$ . Processes of the DPN communicate with each other by consuming data tokens from their input buffers and adding data tokens to the output buffers. Therefore, we define for each process  $p \in \mathcal{P}$ , the tuple of its input buffers inBuf(p) and its output buffers outBuf(p).

In the following, we informally present and elaborate the syntax and the semantics of the general model of a process based on the used subset of CAL.

#### Syntax

The syntax of a process  $p \in \mathcal{P}$  based on the used subset of CAL is illustrated with an abstract example as shown in Listing 2. A process generally consists of a set of input and output buffers and several actions.

```

actor ex() <Type> X_1, \ldots, <Type> X_M \implies <Type>

Y_1, \ldots, <Type> Y_N :

2 label_{\alpha}: action

X_1: [x_{1,1}, \ldots, x_{1,p_1}], \ldots, X_m: [x_{m,1}, \ldots, x_{m,p_m}]

Y_1: [y_{1,1}, \ldots, y_{1,q_1}], \ldots, Y_n: [y_{n,1}, \ldots, y_{n,q_n}]

guard \gamma

3

4

do

\mathbf{5}

y_{1,1} := e_{1,1};

6

7

y_{1,q_1} := e_{1,q_1};

8

9

y_{n,q_n} := e_{n,q_n};

enď

10

11

label_{\alpha}: action

12

X_1: [x_{1,1}, \ldots, x_{1,p_1}], \ldots, X_m: [x_{m,1}, \ldots, x_{m,p_m}]

Y_1: [y_{1,1}, \ldots, y_{1,q_1}], \ldots, Y_n: [y_{n,1}, \ldots, y_{n,q_n}]

guard \gamma

13

dο

14

y_{1,1} := e_{1,1};

15

16

17

y_{1,q_1} := e_{1,q_1};

18

19

:= e_{n,q_n};

y_{n,q_n}

end

20

21 endactor

```

#### Semantics

The abstract example of a process as shown in Listing 2 illustrates the general model based on the used subset of CAL. The head of a process  $p \in \mathcal{P}$  specifies the input buffers inBuf $(p) = (X_1, \ldots, X_M)$  and output buffers outBuf $(p) = (Y_1, \ldots, Y_N)$ , including the type of tokens communicated via the buffer (Line 1). The used CAL subset provides three data types: Boolean, integer and real numbers. The behavior of every process  $p \in \mathcal{P}$  is determined by a set of actions  $\operatorname{actions}(p) = \{\alpha_1, \ldots, \alpha_h\}$ . Actions are preceded by action labels which in the general model need not to be unique, i.e., the same label can be used for more than one action (Lines 2 and 12). The head of an action  $\alpha \in \operatorname{actions}(p)$  specifies for the input buffers in inBuf(p) the number of data tokens to be read (Line 2). It may or may not specify all input buffers in inBuf(p). If the action is fired, these data tokens are consumed from the heads of input buffers and are assigned to the variables  $x_{i,i}$  such that  $x_{i,1}$  is the head of the input buffer  $X_i$ . Analogously, the action interface determines for the output buffers in outBuf(p) the number of data tokens to be written. Thereby, the values  $y_{i,1}, \ldots, y_{i,q_i}$  are added in this order to the tail of output buffer  $Y_i$ . The body of the action is, therefore, a sequence of statements that compute values based on expressions  $e_{i,1}, \ldots, e_{i,q_i}$  and assign them to output variables  $y_{i,1}, \ldots, y_{i,q_i}$  (Lines 5–9). An expression may compose of variables, values, and both arithmetic and Boolean expressions. Since only a subset of inBuf(p)may be used by an action  $\alpha \in \operatorname{actions}(p)$ , we also define  $inAct(\alpha) \subseteq inBuf(p)$  as the subset of input buffers used by that action. Similarly, we define  $outAct(\alpha) \subseteq outBuf(p)$  as the subset of output buffers used by the action. For an action  $\alpha \in \operatorname{actions}(p)$  that requires that input tokens have particular values, an additional condition can be specified using a guard (Line 3) which is a predicate on the tokens of (some prefixes of) the input buffers in  $inAct(\alpha)$ . Since only a subset of  $inAct(\alpha)$  may be used by a guard, we also define  $inGrd(\alpha) \subseteq inAct(\alpha)$  as the subset of input buffers whose values are considered by the guard  $\gamma_{\alpha}$  of action  $\alpha$ .

For the semantics, we consider a domain  $\mathcal{D}$  of values that may be the union of integers, booleans and real numbers. We denote the set of finite sequences on  $\mathcal{D}$  as  $\mathcal{D}^*$  and the set of infinite sequences on  $\mathcal{D}$  as  $\mathcal{D}^{\omega}$ , and the union of both as  $\mathcal{D}^{\infty}$ , i.e.,  $\mathcal{D}^{\infty} := \mathcal{D}^* \cup \mathcal{D}^{\omega}$ . For sequences  $\sigma_1, \sigma_2 \in \mathcal{D}^{\infty}$ , we introduce the prefix ordering  $\sigma_1 \sqsubseteq \sigma_2 :\Leftrightarrow \exists \sigma_3 \in \mathcal{D}^{\infty}$ .  $\sigma_2 = \sigma_1 \cdot \sigma_3$ where  $\sigma_1 \cdot \sigma_3$  means the concatenation of the sequences  $\sigma_1$ and  $\sigma_3$  which demands that  $\sigma_1 \in \mathcal{D}^*$ . The prefix ordering on sequences  $\sigma_1, \sigma_2 \in \mathcal{D}^{\infty}$  is lifted to tuples of sequences  $\sigma_1 = (\sigma_{1,0}, \dots, \sigma_{1,\ell})$  and  $\sigma_2 = (\sigma_{2,0}, \dots, \sigma_{2,\ell})$  in that we demand  $\sigma_{1,i} \sqsubseteq \sigma_{2,i}$  for all  $i \in \{0, \dots, \ell\}$ .

Each process  $p \in \mathcal{P}$  defines a function that maps the consumed input tokens to produced output tokens. This function is determined by a set of actions actions(p) of the process p where the semantics of each action  $\alpha \in actions(p)$  is a function of type  $(\mathcal{D}^*)^m \to (\mathcal{D}^*)^n$  with the following meaning: The action consumes tokens from m input buffers and produces tokens to n output buffers, thus,  $m := |inAct(\alpha)|$ and  $n := |outAct(\alpha)|$ .

Any action  $\alpha \in \operatorname{actions}(p)$  as shown in Listing 2 is enabled iff the following conditions are all satisfied:

- each input buffer X<sub>i</sub> ∈ inAct(α) has enough tokens, i.e.,

X<sub>i</sub> must have at least p<sub>i</sub> many tokens

- each output buffer  $Y_i \in \text{outAct}(\alpha)$  has enough space, i.e.,  $Y_i$  must have at least space for  $q_i$  many tokens

- the guard condition γ which is a condition on the input tokens x<sub>i,j</sub> in inGrd(α) is satisfied

**Listing 2** Abstract example of a process based on the general CAL DPN model.

Fig. 8 A simple example of a non-deterministic process in CAL. The output produced on Y1 depends on the arrival time of tokens on the inputs X1 and X2

The general model of DPN does not impose further restrictions and, therefore, actions consisting of common inputs and/or outputs may be enabled in the same execution, as depicted in Listing 2. As a result, this gives rise to read and write conflicts in buffers, ultimately ending up in nondeterministic behaviors. A read conflict means that two actions are enabled in an execution that read a token from the same input. Whereas, a write conflict means that two actions are enabled in an execution that write a token to the same output. A simple example of a non-deterministic process is illustrated in Fig. 8. It consists of two actions act1 and act2 that consume tokens from different inputs X1 and X2, respectively, and produce tokens to the common output Y1. Depending on the availability of tokens on the inputs, both actions may be enabled in the same execution, and, therefore, may give rise to write conflict in Y1. Hence, the output produced on Y1 depends on the arrival time of tokens on the inputs and, therefore, exhibits a non-deterministic behavior.

We, therefore, demand and use the general CAL DPN model with specific constraints and restrictions to specify the precise dataflow MoCs.

### **Static Dataflow Model**

The static dataflow (SDF) [26] MoC allows one to model static (synchronous) behaviors. It is a more restricted DPN class such that the decision on whether to consume and produce tokens in each execution can be made statically at compile-time. Each execution of a process consumes and produces a fixed number of tokens. The number of tokens consumed or produced on each buffer must be independent of the value as well as the arrival time of data. A process in SDF becomes enabled if and only if all its inputs have required tokens and all its outputs have required space. An enabled process may fire, and once fired, consumes the statically specified number of tokens from its inputs and produces the statically specified number of tokens to its outputs.

We demand and assume certain restrictions on the general DPN model to represent the SDF MoC. In the following, we present an abstract example of a static process based on the SDF MoC and informally illustrate its semantics.

#### Syntax

The syntax of a static process in SDF is illustrated with an abstract example as shown in Listing 3.

```

1 actor SDF() <Type> X_1, \ldots,<Type> X_m => <Type>

Y_1, \ldots, <\mathsf{Type} > Y_n:

2 label_{\alpha_1}: action

X_1 : [x_{1,1}, \dots, x_{1,p_1}], \dots, X_m : [x_{m,1}, \dots, x_{m,p_m}]

---->

Y_1: [y_{1,1}, \ldots, y_{1,q_1}], \ldots, Y_n: [y_{n,1}, \ldots, y_{n,q_n}]

3

guard \gamma_{\alpha_1}

\mathbf{4}

do

y_{1,1} := e_{1_{1,1}};

5

6

y_{1,q_1} := e_{1_{1,q_1}};

7

8

y_{n,q_n} := e_{1_{n,q_n}};

9

10

end

11

\begin{array}{ccc} & & & & \\ 12 & label_{\alpha_h} \colon \texttt{action} \\ & & & X_1 : [x_{1,1}, \dots, x_{1,p_1}], \dots, X_m : [x_{m,1}, \dots, x_{m,p_m}] \end{array}

Y_1: [y_{1,1}, \ldots, y_{1,q_1}], \ldots, Y_n: [y_{n,1}, \ldots, y_{n,q_n}]

guard \bar{\gamma}_{\alpha_h}

13

do

14

y_{1,1} := e_{h_{1,1}};

15

16

17

y_{1,q_1} := e_{h_{1,q_1}};

18

19

y_{n,q_n} := e_{h_{n,q_n}};

end

20

21 endactor

```

Listing 3 Abstract example of a process in SDF.

### Semantics

A process  $p \in \mathcal{P}$  in SDF consists of a set of actions actions $(p) = \{\alpha_1, \dots, \alpha_h\}$ . The action labels need to be unique, i.e., the same label must not be used for more than one action (Lines 2 and 12). For each action  $\alpha_i$ , we define its guard  $\gamma_{\alpha_i}$ . Each action  $\alpha_i \in \operatorname{actions}(p)$  specifies for all input buffers inBuf(p) and all output buffers outBuf(p) the number of tokens to be read and written, respectively. Thus, the input and output buffers are always same across all actions i.e., inAct $(\alpha_1) = \dots = \operatorname{inAct}(\alpha_h)$  and outAct $(\alpha_1) = \dots = \operatorname{outAct}(\alpha_h)$ . Second, the number of tokens to be consumed and the number of tokens to be produced are always same for the same input and output buffers, respectively, across all actions. This restricts the execution of processes to fixed consumption and production rates.

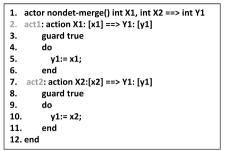

**Fig. 9** The static if-then-else (ITE) node: a simple example of a static process in SDF. An example behavior is illustrated with a set of input values and the computed output values as shown inside arrows

Regardless of which action is executed, the same number of tokens are consumed and produced in the same buffers in each firing of a process. Moreover, we demand that the guard conditions should always be mutually exclusive across actions. This ensures that for each execution of a process, the actions will never compete for an execution. Hence, in each execution of a process only a specific action is fired whose guard is enabled.

#### **Execution of Actions**

Each time a process  $p \in \mathcal{P}$  is triggered for an execution, a particular action is executed, mainly dependent on which guard is enabled. The guards of actions  $\operatorname{actions}(p)$  are always evaluated sequentially in the same order of their actions definitions. Since all actions in a process have same input buffers with same consumption rates, hence for any action  $\alpha_i \in \operatorname{actions}(p)$ , the specified fixed number of tokens are first consumed from all input buffers  $\operatorname{inAct}(\alpha_i) = \operatorname{inBuf}(p)$ . Finally, the enabled action is fired whose guard is true. Upon firing, the defined computations are performed and the specified fixed number of tokens are produced to all output buffers  $\operatorname{outAct}(\alpha_i) = \operatorname{outBuf}(p)$ .

### Triggering Processes for Execution

Each process  $p \in \mathcal{P}$  in SDF is triggered for an execution if and only if all input buffers  $inAct(\alpha_i)$  of an action  $\alpha_i \in actions(p)$  have enough input tokens and all output buffers  $outAct(\alpha_i)$  of that action have enough space. The process shown in Listing 3 is triggered for an execution iff for any action  $\alpha_i$ , each input buffer  $X_j \in inAct(\alpha_i)$  has at least  $p_j$ many tokens and each output buffer  $Y_j \in outAct(\alpha_i)$  has at least space for  $q_j$  many tokens.

#### SDF Process Example

A simple example of the static if-then-else (ITE) operation is illustrated in Fig. 9. In each execution, the ITE process consumes a token each from all three inputs and produces a token to its only output. It consists of two actions i.e., *act1* and *act2*, having same inputs X1, X2 and X3, and the same output Y (Lines 2 and 7). Both actions use the input XI for the guard with mutually exclusive guard conditions (Lines 3 and 8). In each execution, depending on which guard is enabled, either *act1* or *act2* fires for an execution. ITE is only triggered for an execution if there is a token available in all three inputs XI, X2 and X3 and if there is space available for a token to be produced at the output Y. The tokens are denoted by small letters x1, x2, x3 and y.

### Kahn Process Networks Model

Kahn process networks (KPNs) [21] are dynamic DPNs where processes can consume and produce different number of tokens in every firing depending on the history of the consumed tokens and also on the tokens to be consumed. KPNs exhibit latency-insensitive deterministic behaviors that do not depend on the timing or the execution order of the processes. The KPN MoC is typically specified with the following restrictions and properties:

- processes are not allowed to test input buffers for the existence of tokens

- reading from input buffers is blocking, and writing to output buffers is non-blocking

- processes must implement deterministic sequential functions

- processes do not need all of their inputs to get triggered for execution

Based on these restrictions/properties, it can be implied that a process in KPN can be any sequential program where the firing rules can be tested sequentially in a predefined order in each execution using blocking reads [27]. This reflects the ability to uniquely consume the inputs in each firing without timing information provided by the input signals. A KPN process is only triggered for execution if the exact information on inputs required to produce the output is available. A process, therefore, becomes enabled if the required values on inputs are available to perform the computation and produce the output. A process once enabled, may fire, and once fired, it may consume different number of tokens from different inputs based on the history of the consumed tokens. The KPN MoC can capture both static as well as sequential behaviors. Since buffers with unbounded capacity cannot be realized in real implementations, the used KPN model only supports blocking write. However, since the starting point of this work is the desynchronized models, desynchronization preserves properties like deadlock-freedom and bounded memory usage that are otherwise difficult to ensure in KPNs [2].

Next, we present an abstract example of a sequential process based on the KPN MoC and illustrate its semantics.

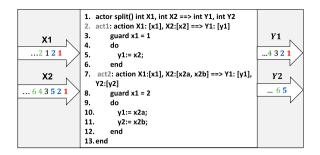

**Fig. 10** The split node: a simple example of a sequential process in KPN. An example behavior is illustrated with a set of input values and the computed output values as shown inside arrows

#### Syntax

The syntax of a sequential process in KPN is illustrated with an abstract example as shown in Listing 4.

```

1 actor KPN() <Type> X_1, \ldots, <Type> X_M \implies <Type>

Y_1, \ldots, <\mathsf{Type} > Y_N:

2 label_{\alpha_1}: action

X_1 : [x_{1,1}, \dots, x_{1,p_1}], \dots, X_m : [x_{m,1}, \dots, x_{m,p_m}]

Y_1: [y_{1,1}, \ldots, y_{1,q_1}], \ldots, Y_n: [y_{n,1}, \ldots, y_{n,q_n}]

guard \gamma_{lpha_1}

з

do

4

y_{1,1} := e_{1_{1,1}};

5

6

y_{1,q_1} := e_{1_{1,q_1}};

7

8

9

y_{n,q_n} := e_{1_n,q_n};

end

10

11

\begin{array}{c} \begin{array}{c} \begin{array}{c} 11 \\ 12 \end{array} \\ 12 \hspace{0.5mm} label_{\alpha_{h}} \colon \texttt{action} \\ X_{1} : [x_{1,1}, \ldots, x_{1,f_{1}}], \ldots, X_{u} : [x_{u,1}, \ldots, x_{u,f_{u}}] \\ & Y_{\dots} : [u_{n,1}, \ldots, u_{n,f_{u}}] \end{array}

\implies Y_1: [y_{1,1}, \dots, y_{1,g_1}], \dots, Y_v: [y_{v,1}, \dots, y_{v,g_v}]

guard \gamma_{\alpha_h}

13

14

do

y_{1,1} := e_{h_{1,1}};

15

16

y_{1,g_1} := e_{h_{1,g_1}};

17

18

19

y_{v,g_v} := e_{h_{v,g_v}};

end

20

21 endactor

```

Listing 4 Abstract example of a process in KPN.

#### Semantics

A process  $p \in \mathcal{P}$  in KPN consists of a set of actions actions $(p) = \{\alpha_1, \dots, \alpha_h\}$ . The action labels need to be unique, i.e., the same label must not be used for more than one action (Lines 2 and 12). For each action  $\alpha_i$ , we define its guard  $\gamma_{\alpha_i}$ . Each action  $\alpha_i \in \operatorname{actions}(p)$  specifies for the input buffers inAct( $\alpha_i$ )  $\subseteq$  inBuf(p) and the output buffers  $outAct(\alpha_i) \subseteq outBuf(p)$  the number of tokens to be read and written, respectively. In general, the input and output buffers can be different across different actions. However, since processes in KPN consist of sequential functions, we demand that all actions in a process must have at least one common input. This implies that  $inAct(\alpha_1) \cap ... \cap inAct(\alpha_k) \neq \{\}$ . Moreover, we demand that the guard conditions are always mutually exclusive across actions. This ensures that for each execution of a process, the actions will never compete for an execution. Hence, in each firing of a process only a specific action is executed mainly dependent on which guard is enabled. Second, this enables the execution of processes with dynamic consumption rates and dynamic production rates, mainly dependent on which guards are enabled on each execution.

#### Evaluation and Execution of Actions

As discussed, the KPN MoC does not allow processes to test input buffers for the existence of tokens. A process is only triggered for execution if the exact information on inputs required to execute an action is available. Therefore, each time a process  $p \in \mathcal{P}$  is triggered for an execution, a particular action  $\alpha_i \in \operatorname{actions}(p)$  is executed whose guard  $\gamma_{\alpha_i}$  is enabled. The enabled action  $\alpha_i$ , once fires, consumes a finite number of tokens from the input buffers inAct $(\alpha_i)$ and produces a finite number of tokens to the output buffers outAct $(\alpha_i)$  as specified for that action.

#### Triggering Processes for Execution

Since processes in KPNs consist of sequential programs, the availability of tokens on the inputs, the availability of space on the outputs, and the guards can be evaluated sequentially in a predefined order of their actions definitions. Each process  $p \in \mathcal{P}$  is triggered for an execution if there exists one particular action  $\alpha_i \in \operatorname{actions}(p)$  having: enough input tokens in  $inAct(\alpha_i)$ , required values on the guarded inputs in  $Grd(\alpha_i)$ , and enough space in  $outAct(\alpha_i)$ . For instance, the process shown in Listing 4 is triggered for an execution when for a particular action (say  $\alpha_h$ ), each input buffer  $X_i \in inAct(\alpha_h)$  has at least  $f_i$  many tokens, each output buffer  $Y_i \in \text{outAct}(\alpha_h)$  has at least space for  $g_i$  many tokens, and the guard  $\gamma_{\alpha_{L}}$  is true. In case if one of the inputs does not have enough tokens, the process is blocked (i.e., the blocking behavior of KPN) until sufficient tokens are available on that input.

#### KPN Process Example

A simple example of a sequential process, namely the *split* node is illustrated in Fig. 10 that splits a single input channel to a number of individual output channels. The split node consists of two actions *act1* and *act2* that depending on the value of a token at the input XI splits the tokens from the

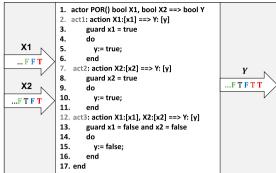

**Fig. 11** The parallel OR node: a simple example of a well-behaved parallel process in DDF. An example behavior is illustrated with a set of input values and the computed output values as shown inside arrows

input X2 to outputs Y1 and Y2. The guards are composed of mutually exclusive conditions (Lines 3 and 8). Both actions declare the input X2 with different consumption rates (Lines 2 and 7). The action act2 has an additional output Y2. In each execution, depending on which guard is enabled, either act1 or act2 fires for an execution. In the case where act1 fires, a single token each is consumed from X1 and X2, and a single token is produced to Y1 (Line 5). On the contrary, when act2 fires, a single token is consumed from X1, two tokens are consumed from X2 and a token each is produced to Y1 and Y2 (Lines 10-11). Hence, in each execution, a different number of tokens can be consumed from the input X2 and a different number of tokens can be produced to outputs Y1 and Y2. The split node is only triggered for an execution if there exists one action i.e., either act1 or act2, having required number of tokens in X1 and X2, required space in outputs Y1 and Y2, and required values on the input X1.

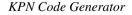

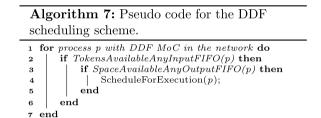

### **Dynamic Dataflow Model**

The dynamic dataflow (DDF) also sometimes referred to as the non-determinate dataflow is a dynamic DPN class that allows one to model dynamic and asynchronous processes. It offers a more generalized data dependent and asynchronous execution semantics than the KPN MoC. In particular, the DDF MoC allows one to model processes with parallel programs consisting of concurrent and independent computations where more than one action can be executed in each firing. This generalization results in higher expressiveness and flexibility, however, may lead to non-deterministic behaviors, e.g., a non-determinate merge [27]. We use a variant of the DDF MoC that only supports concurrent and independent actions with specific restrictions. It can be used to model well-behaved parallel nodes that exhibit deterministic behaviors, e.g., the parallel OR (POR) node as illustrated in Fig. 11 (discussed in the next subsection).

```

actor DDF() <Type> X_1, \ldots, <Type> X_m, \ldots, <Type

> X_M \implies \langle \mathsf{Type} > Y_1, \dots, \langle \mathsf{Type} > Y_n, \dots, \langle

Type Y_N :

2 label_{\alpha_1}: action

X_1 : [x_{1,1}, \dots, x_{1,p_1}], \dots, X_m : [x_{m,1}, \dots, x_{m,p_m}]

==>

Y_1: [y_{1,1}, \ldots, y_{1,q_1}], \ldots, Y_n: [y_{n,1}, \ldots, y_{n,q_n}]

guard \gamma_{lpha_1}

3

4

do

\mathbf{5}

y_{1,1} := e_{1_{1,1}};

6

y_{1,q_1} := e_{1_{1,q_1}};

7

8

9

y_{n,q_n} := e_{1_{n,q_n}};

10

end

11

label_{\alpha_k}: action X_{m+1}: [x_{m+1,1}, \ldots, x_{1,p_{m+1}}], \ldots,

12

\tilde{X}_M : [x_{M,1}, \dots, x_{M,p_M}] = >

Y_{n+1}: [y_{n+1,1}, \ldots, y_{n+1,q_{n+1}}], \ldots,

Y_N:[y_{N,1},\ldots,y_{N,q_N}]

guard \gamma_{\alpha_k}

13

14

do

y_{n+1,1} := e_{k_{n+1,1}};

15

16

17

y_{n+1,q_{n+1}} := e_{k_{n+1},q_{n+1}}

18

y_{N,q_N} := e_{k_{N,q_N}};

19

20

end

21

label_{\alpha_h}: \underset{X_m: [x_{m,1}, \ldots, x_{m,f_m}] \ldots, }{\operatorname{action} X_1: [x_{m,1}, \ldots, x_{m,f_m}] \ldots}

22

X_M : [x_{M,1}, \ldots, x_{M,g_M}] \Longrightarrow

Y_1: [y_{1,1}, \dots, y_{1,q_1}], \dots, Y_n: [y_{n,1}, \dots, y_{n,q_n}]

Y_N:[y_{N,1},\ldots,y_{N,q_N}]

guard \gamma_{lpha_h}

23

^{24}

do

^{25}

y_{1,1} := e_{h_{1,1}};

\mathbf{26}

y_{1,q_1} := e_{h_{1,q_1}};

27

28

y_{N,q_N} := e_{h_{N,q_N}};

29

30

end

31

endactor

```

Listing 5 Abstract example of a process in DDF.

The considered variant of DDF MoC offers a more flexible semantics where each process becomes enabled for an execution if only one of its inputs has required tokens and only one of its outputs has required space. The decision on whether to consume/produce tokens and to execute each action of an enabled process is made dynamically at runtime when that particular process is triggered for an execution. A process once enabled, may fire, and once fired, it may trigger multiple actions for execution. A process can produce and consume different number of tokens in every firing. The considered variant of DDF MoC can capture static, sequential and well-behaved parallel processes. In the following, we present an abstract example of a well-behaved parallel process based on the DDF MoC and informally illustrate its semantics.

#### Syntax

The syntax of a well-behaved parallel process in DDF is illustrated with an abstract example as shown in Listing 5.

#### Semantics

A process  $p \in \mathcal{P}$  in DDF consists of a set of actions  $actions(p) = \{\alpha_1, \dots, \alpha_h\}$ . The action labels need to be unique, i.e., the same label must not be used for more than one action (Lines 2, 12 and 22). For each action  $\alpha_i$ , we define its guard  $\gamma_{\alpha}$ . Different actions in actions(*p*) may specify completely different input and output buffers e.g.,  $inAct(\alpha_1) \cap inAct(\alpha_k) = \{ andoutAct(\alpha_1) \cap outAct(\alpha_k) = \{ \} \}$ This enables the modeling of processes with independent actions consisting of completely different inputs and outputs. Moreover, different actions in actions(p) may also specify common input and output buffers e.g.,  $inAct(\alpha_1) \cap inAct(\alpha_k) \neq \{ \} andoutAct(\alpha_k) \cap outAct(\alpha_k) \neq \{ \}.$ The associated number of token variables (i.e., token consumption rates) of common input buffers can be different across actions. Multiple actions may fire in the same execution of a process. However, we demand that these firings must be consistent and do not give rise to non-deterministic behaviors. In particular, we demand that the guard conditions of actions with common input buffers are always mutually exclusive. Hence, in each firing of a process only a specific action from all actions having at least one common input buffer is executed whose guard is enabled.

This ensures that for each execution of a process, the actions with common input buffers will never compete for an execution for any set of tokens. Moreover, for actions with at least one common output buffer, we demand that each action upon firing produces the same sequence of tokens at the common output buffer. Hence, the firing of actions with common output buffers do not lead to different output streams. Altogether, these restrictions enable the execution of processes consisting of well-behaved parallel programs with dynamic consumption rates and dynamic production rates, mainly dependent on which guards are enabled on each execution. An example of a well-behaved parallel node exhibiting such a behavior is illustrated in Fig. 11.

#### Evaluation and Execution of Actions

Each action  $\alpha_i \in \operatorname{actions}(p)$  of a process  $p \in \mathcal{P}$  is evaluated for an execution dynamically when that particular process is triggered for an execution. Each action  $\alpha_i$  fires for an execution iff: there are enough tokens available in inAct( $\alpha_i$ ), enough space available in outAct( $\alpha_i$ ), and the required values on the guarded inputs  $inGrd(\alpha_i)$  are available, i.e., the guard  $\gamma_{\alpha_i}$  is true. When the action  $\alpha_i$  fires, it consumes a finite number of tokens from  $inAct(\alpha_i)$  and produces a finite number of tokens to  $outAct(\alpha_i)$ .

Since the actions are evaluated dynamically only after a particular process is triggered for an execution, there may be a case when for an action  $\alpha_i$ , although the guard  $\gamma_{\alpha_i}$ is true, however, either at least one of the input buffers in inAct $(\alpha_i)$  does not have enough tokens, or at least one of the output buffers in outAct $(\alpha_i)$  does not have enough space. In this case, neither the input tokens are consumed from inAct $(\alpha_i)$ , nor the output tokens are produced to outAct $(\alpha_i)$ . Instead, the tokens are preserved in their respective input buffers.

#### Triggering Processes for Execution

As the decision to execute each action of a process and consume/produce data tokens is made dynamically at runtime, when that process is triggered for an execution. Therefore, each process  $p \in \mathcal{P}$  is triggered for an execution if there exists at least one input buffer  $X_j \in inAct(\alpha_i)$  having enough input tokens and there exists at least one output buffer  $Y_j \in inAct(\alpha_i)$  having enough space. For instance, the process shown in Listing 5 is triggered for an execution when for a particular action (say  $\alpha_1$ ), any input buffer  $X_j \in inAct(\alpha_1)$  has at least  $p_j$  many tokens and any output buffer  $Y_i \in outAct(\alpha_1)$  has at least space for  $q_i$  many tokens.

#### DDF Process Example

A simple example of the parallel OR (POR) node is illustrated in Fig. 11 that performs the logical OR operation on two Boolean inputs. The POR node consists of three actions act1, act2 and act3 that depending on the values of tokens in either or both of the inputs X1 and X2 produces tokens in the only output Y. The actions act1 and act3 share a common input X1 (Lines 2 and 12). The actions act2 and act3 share a common input X2 (Lines 7 and 12). All actions share the same output Y (Lines 2, 7 and 12). In each execution, depending on which guards are enabled, either one or both of the actions act1, act2 can be fired. In case if both the actions are enabled, a token each is produced to the output Y by both actions (Lines 5 and 10). Since they share a common output, hence, the same sequence of tokens is produced at the output Y by both actions. In contrast, if the guard is true for act3, the actions act1, act2 become disabled where only the action act3 is fired. Therefore, the actions with common inputs never compete for firing in any execution of the process. The POR node is only triggered for an execution if there is a token available in at least one of the inputs i.e., either X1 or X2, and there is a space available for one token to be produced in the only output Y.

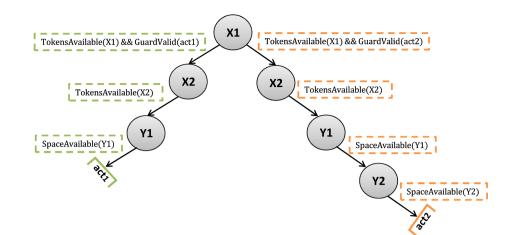

Fig. 12 The proposed synthesis tool chain is composed of two main parts: the *back-end* features the specialized code generators for the supported dataflow MoCs. The *runtime system* organized in a host and kernels program model schedules and maps the modeled system on the target hardware

# Synthesis: The Toolchain

In this section, we present the synthesis tool chain which is depicted in Fig. 12. It offers a set of tools that work together to finally implement the CAL DPNs on commercial off-the-shelf (COTS) target hardware. The tool chain is composed of two main parts: a special *back-end* comprising of specialized code generators for particular dataflow MoCs and the *runtime system*. Each code generator generates an OpenCL kernel for each process based on the underlying dataflow MoC. Second, the runtime system is organized in a centralized host and kernels program model, built under the OpenCL abstraction. The host features different components including the *Runtime-Manager* that schedule and deploy processes (generated kernels) on the target hardware.

### Back-end

The back-end is designed to work in two different modes, namely the manual mode and the auto mode. In the manual mode, the back-end targets homogeneous implementations based on a specific user given dataflow MoC. In the auto mode, the back-end automatically classifies the processes into three categories mainly according to their kinds of behaviors that determine the dataflow MoCs. This classification of different kinds of behaviors involves: the static ones based on the static dataflow (SDF) MoC, the sequential ones based on the Kahn process network (KPN) MoC, and the parallel ones based on a variant of the dynamic dataflow (DDF) MoC. As a result, the back-end provides three different specialized code generators for particular dataflow MoCs: one for the SDF MoC, second for the KPN MoC, and finally for the used DDF MoC. We identify the kinds of behaviors of processes during desynchronization based on a succinct formalization of input/output (I/O) firing rules of synchronous components [38, 39]. The identified dataflow MoC of each process is divulged to the synthesis phase through the network description file.

In the following, we present the specialized code generators based on the supported dataflow MoCs.

### **Code Generators: Kernel Code Generation**

Each code generator is determined by the underlying semantics of the used dataflow MoC. It, therefore, generates an OpenCL kernel for each process based on the underlying dataflow MoC. This section presents the schemes employed for generating OpenCL kernel code based on all the supported dataflow MoCs. Moreover, we also illustrate the generated kernel code for each supported dataflow MoC based on the CAL models presented in Figs. 9, 10 and 11.

Each code generator generates kernel code in two segments: First, the OpenCL specific code is targeted which involves the generation of the kernel header, the declaration of used inputs and outputs, and most importantly, the generation of generic kernel code that enables the host to dispatch multiple executions of the kernel on the device. This code segment is more or less same for all used dataflow MoCs. The second segment targets the code generation based on the underlying semantics of the used dataflow MoC. We mainly present the schemes designed for generating code for the latter segment. The former segment is explained in detail with the generated kernel code examples.

| $\mathbf{Al}$ | gorithm 1: Pseudo code for SDF                                                                                                                                                                                                                    |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ker           | nel code generation of a process $p$ .                                                                                                                                                                                                            |  |  |  |

|               | onsumeTokens(inBuf(p));<br><b>preach</b> action $\alpha$ in p <b>do</b><br>EvaluateGuard( $\gamma_{\alpha}$ );<br><b>if</b> GuardValid( $\gamma_{\alpha}$ ) <b>then</b><br>PerformComputations( $\alpha$ );<br>ProduceTokens(outAct( $\alpha$ )); |  |  |  |

| 7             | 7 end                                                                                                                                                                                                                                             |  |  |  |

| 8 ei          | s end                                                                                                                                                                                                                                             |  |  |  |

### SDF Code Generator

In SDF, it is statically determined that each firing of a process consumes/produces fixed number of tokens. A process in SDF is, therefore, simply scheduled by the host for execution if there is enough data available in all inputs and if there is enough space available in all outputs. The guards of actions are evaluated within kernels on the device side. The SDF code generation is relatively straightforward and is illustrated by the pseudo code given in Algorithm 1.

For a static process, the proposed scheme works as follows: First, the code is generated to consume tokens from all input buffers of the process (Line 1). The algorithm then iterates through the set of modeled actions in the order of their definitions (Line 2) where for each action, it proceeds as follows: First, the code is generated to evaluate the guard (Line 3). Next, the code is generated for the case if the guard is fulfilled (Lines 4–7). To this end, the code to perform the modeled computations is generated (Line 5), and then to produce the final output (Line 6). The generated kernel for a static process *ITE* as shown in Fig. 9 is listed in Listing 6.

```

__kernel void ITE ( __global fifo_t* X1

__global fifo_t* X2 , __global fifo_t* X3,

__global fifo_t* Y, int blockSize)

2

{

/* Declarations for All Inputs and Outputs */

3

__private int seq_X1[1];

4

__private int seq_X2[1];

5

__private int seq_X3[1];

6

__private int seq_Y[1];

int* x1_act1 = &seq_X1[0];

8

int* x1_act2 = &seq_X1[0];

9

int* x2_act1 = &seg_X2[0];

10

int* x2_act2 = &seg_X2[0]:

11

int* x3_act1 = &seq_X3[0];

12

int* x3_act2 = &seq_X3[0];

13

int* y_act1 = &seq_Y[0];

14

int* y_act2 = &seq_Y[0];

15

* Generic Kernel Code *

16

int gid = get_global_id(0) * blockSize:

17

for (int x = 0; x < blockSize; x++) {

/* SDF Specific Kernel Code */</pre>

18

19

fifoRead(X1, seq_X1, 1, gid);

\mathbf{20}

^{21}

fifoRead(X2, seq_X2, 1, gid)

fifoRead(X3, seq_X3, 1, gid);

^{22}

if(*x1_act1 \ge 0)

^{23}

y_act1 = *x2_act1;

^{24}

fifoWrite(Y, seq_Y, 1, gid);

^{25}

^{26}

27

else if(*x1_act2 < 0 ) {

*y_act2 = *x3_act2;

28

fifoWrite(Y, seq_Y, 1, gid);

29

30

}

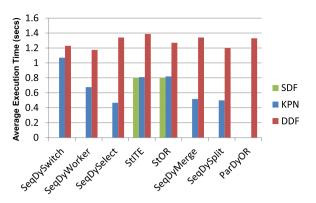

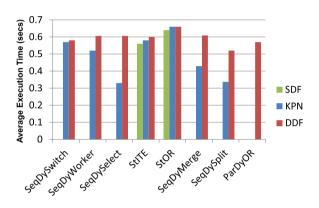

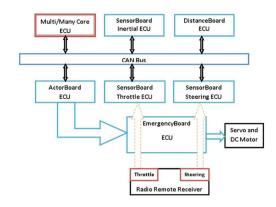

31