#### Jochen Barthel

Berichte aus dem Lehrstuhl für Messtechnik und Sensorik Band 15

Herausgeber: Prof. Dr.-Ing. Jörg Seewig

Jochen Barthel

Modular High Voltage DC/DC Converters and Converter Control

Berichte aus dem Lehrstuhl für Messtechnik und Sensorik Band 15

Herausgeber: Prof. Dr.-Ing. Jörg Seewig

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

Berichte aus dem Lehrstuhl für Messtechnik und Sensorik - Band 15

Herausgeber: Prof. Dr.-Ing. Jörg Seewig

Lehrstuhl für Messtechnik und Sensorik

Fachbereich Maschinenbau und Verfahrenstechnik

Technische Universität Kaiserslautern

Gottlieb-Daimler-Straße 67663 Kaiserslautern

Verfasser: Jochen Barthel

Verlag: Technische Universität Kaiserslautern

Druck: Technische Universität Kaiserslautern

Hauptabteilung 5 | Abteilung 5.6 Foto-Repro-Druck

D-386

© Jochen Barthel · Kaiserslautern 2022

Alle Rechte vorbehalten, auch das des auszugsweisen Nachdrucks, der auszugsweisen oder vollständigen Wiedergabe (Photographie, Mikroskopie), der Speicherung in Datenverarbeitungsanlagen und das der Übersetzung.

Als Manuskript gedruckt. Printed in Germany.

ISSN 2365-9742 ISBN 978-3-95974-192-7

# Modular High Voltage DC / DC Converters and Converter Control

Vom Fachbereich Maschinenbau und Verfahrenstechnik der Technischen Universität Kaiserslautern zur Erlangung des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

genehmigte

Dissertation

von

Dipl.-Ing. Jochen Barthel aus Kirchheimbolanden

Dekan: Prof. Dr.-Ing. Tilmann Beck Vorsitzender: Prof. Dr.-Ing. Peter Pickel Berichterstatter: Prof. Dr.-Ing. Jörg Seewig

Prof. Dr.-Ing. Daniel Görges

Tag der mündlichen Prüfung: 04. November 2022

## Acknowledgement

This thesis was created while working as research associate at the Institute for Measurement and Sensor-Technology (MTS) at the University of Kaiserslautern, where I was a team member of the publicly funded project *Sustainable Energy Supply for Agricultural Machinery* (SESAM).

First, I'd like to express my special thanks to my advisor *Prof. Dr.-Ing. Jörg Seewig* for giving me the opportunity to work at his Institute as well as for his advice and support to every respect during my time at the Institute. This leads directly to *Prof. Dr.-Ing. Daniel Goerges*, wo agreed to take over one of the thesis' reports without hesitation, when asked by Jörg. His advice was always extremely valuable to me. My thanks also belong to *Prof. Dr.-Ing. Peter Pickel* from *John Deere* for chairing the dissertation's committee and for leading the SESAM consortium.

Next, I'd like to thank my student, who contributed to this thesis with their work. Namely, Marcel Baßler, Kevin Kadel, Wilber Mejia, Zai Zhang, Tommy José Langers, Kilian Jung, Zijin Lin, Remko Müller, Laura Schradt and Félix Aguirre. Their contribution to this thesis is specially valued.

Special thanks go to my colleagues during my time at MTS for the great scientific exchange in all its variants. Among all, I'd like to specially mention Marc-Alexandre Favier for our joint time at SESAM, Dr.-Ing. Gerhard Stelzer for his support and Dr.-Ing. Paaranan Sivasothy for our discussions while office-sharing and after my time at MTS. Further, especially mentioned need to be Dr.-Ing. Steve Armand Fankem Fankem, Dr.-Ing. Frederic Ballaire, Daniel Broschart, Dr.-Ing. Sebastian Pick, Sebastian Rief, Dr.-Ing. Kiarash Sabzewari, Dr.-Ing. Roland Werner and Dr.-Ing. Khang-Zhun Yeap. Besides the professional interaction, everything from irrelevant/fun talk to private activities need to be highlighted and were key to making working at the university as great as it was.

Here, I'd like to place my thanks to *Renate Wiedenhöft* (MEC) and *Marie Demuth* (MTS) for their administrative work at the institutes.

A great part in putting this thesis's text to a meaningful and readable state is due to *Prof. Dr.-Ing. habil. Matthias Eifler* and my aunt *Ute Barthel-Knoll*, who took over the ungrateful job of prove reading to a scientific and orthographic respect. Their feedback is most highly appreciated.

In this relation, *Philipp Armecke* and *Stefan Tomoschat* need to be mentioned, both are dear friends. We spend hours, discussing various thesis-related topics from theoretical up to practical implementation. Their vast knowledge as electrical engineer and electronics technician is truly valued.

My gratefulness dresses my family, my parents *Werner* and *Sigrid* and my little sister *Regina*. Thank you for all your support and everything. Finally, I say thank you for all to *Eva*.

Stuttgart, in December 2022

Jochen Barthel

### **Abstract**

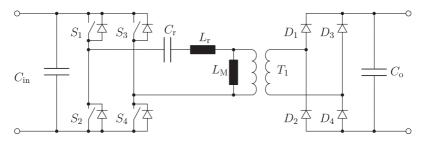

Efforts in decarbonization lead to electrification, not only for road vehicles but also in the sector of mobile machines. Aside from batteries, those machines are electrified by tethering systems, nowadays featuring an AC low voltage system. Those systems are applied, e.g., to underground load haul dumpers with short tethering lines and low machine power. To expand tethering to further markets as agricultural machinery, this work proposes an HVDC tethering system allowing higher machine power and transmission length due to thinner, lighter tethering lines. The HVDC voltage is converted by distribution over a number of series connected DC/DC converters. Less blocking voltage on the semiconductors allows faster switching technology to reduce the converters' weight and volume. Since comparable concepts exist for offshore wind farms connectivity, its applicability for this is discussed. A full bridge inverter/rectifier LLC resonance DC/DC converter is presented for the modules. A switched LTI converter model is developed and a Common Quadratic Lyapunov Function (CQLF) is computed for prove of stability. The converter control features soft startup and voltage control over all modules. The concepts are validated by simulation and on a scaled prototype.

## Kurzfassung

Die Bemühungen zur Dekarbonisierung führen zur Elektrifizierung, nicht nur bei Straßenfahrzeugen, sondern auch bei mobilen Arbeitsmaschinen. Neben Batterien werden diese durch Schleppleitungssysteme mit AC Niederspannung elektrifiziert. Solche Systeme werden z. B. bei Untertage-Radladern mit kurzen Leitungen und geringer Leistung eingesetzt. Um Schleppleitungen in weitere Märkte wie Landmaschinen auszuweiten, wird eine HVDC-Anbindung vorgeschlagen, die durch dünnere, leichtere Leitungen höhere Maschinenleistung und Übertragungslänge erlaubt. Die hohe Leitungsspannung wird durch in Reihe geschalteten DC/DC-Wandler aufgeteilt und gewandelt. Geringe Sperrspannung ermöglicht den Einsatz schnell schaltender Halbleiter, um Wandler-Gewicht und -Volumen zu reduzieren. Da vergleichbare Konzepte für Offshore-Windparks existieren, wird seine Anwendbarkeit für diese diskutiert. Für die Module wird ein Vollbrücken-LLC Resonanzwandler vorgestellt. Ein switched LTI Modell wird abgeleitet und die Stabilität durch eine Common Quadratic Lyapunov Function (CQLF) nachgewiesen. Die Spannungsregelung enthält eine Softstart Methode und Regelung über alle Module. Die Konzepte werden simulativ und prototypisch validiert.

Contents

## Contents

| Lis | st of A | Abbreviations                                                 | X   |

|-----|---------|---------------------------------------------------------------|-----|

| Lis | st of I | Latin Symbols                                                 | xi  |

| Lis | st of ( | Greek Symbols                                                 | xvi |

| 1.  | Intr    | oduction                                                      | 1   |

|     | 1.1.    | Electrical Energy Transmission                                | 2   |

|     |         | Electrical Energy Conversion                                  |     |

|     |         | Motivation and Objectives of this Publication                 |     |

| 2.  | State   | e-of-the-Art of Resonant Switched DC / DC Power Converters    | 7   |

|     | 2.1.    | Zero Voltage / Zero Current Switching                         | 7   |

|     |         | 2.1.1. Switching behavior and losses in IGBTs                 | 8   |

|     |         | 2.1.2. Zero Current Switching                                 | 11  |

|     |         | 2.1.3. Zero Voltage Switching                                 | 12  |

|     | 2.2.    | Resonant Switched Converters                                  | 13  |

|     |         | 2.2.1. Single Resonance Circuits                              | 15  |

|     |         | 2.2.2. Dual Resonance Circuits                                |     |

|     |         | 2.2.3. Triple Resonance Circuits                              | 19  |

|     | 2.3.    | LLC Converters                                                | 19  |

|     |         | 2.3.1. Operation Principles of LLC Converters                 |     |

|     |         | 2.3.2. First Harmonic Approximation                           | 23  |

|     | 2.4.    | Control Techniques for DC/DC Converters                       | 27  |

|     |         | 2.4.1. Trajectory Planning and Tracking for State Transitions |     |

|     | 2.5.    | Fundamentals of Switched Systems                              | 31  |

|     |         | 2.5.1. Continuous Time Switched Linear Systems                | 32  |

|     |         | 2.5.2. Stability Analysis of Switched Linear Systems          | 32  |

|     | 2.6.    | Contribution to the State-of-Science                          | 34  |

| 3.  | Mod     | lular High Voltage DC / DC Power Converter                    | 35  |

|     | 3.1.    | Conception of a DC/DC Converter for High Voltage              | 36  |

vi Contents

|    | 3.2. | Conce   | ption of a Module for a High Voltage DC/DC Converter               | 39  |

|----|------|---------|--------------------------------------------------------------------|-----|

|    |      | 3.2.1.  | Design Considerations for the Inverter and Rectifier               | 40  |

|    |      | 3.2.2.  | Operating Space and Conditions of the Converter Module             | 42  |

|    |      | 3.2.3.  | Design Considerations for the Transformer and the Resonance        |     |

|    |      |         | Components                                                         | 44  |

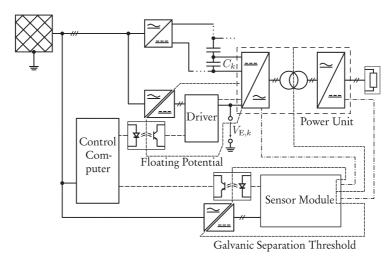

|    |      | 3.2.4.  | Galvanic Isolation and Handling of Different Electrical Potentials | 48  |

|    | 3.3. | Applica | ation Scenario I: HV DC/DC Converters for Grid Connection          |     |

|    |      | of Offs | shore Wind Farms                                                   | 51  |

|    | 3.4. | Applica | ation Scenario II: HV DC / DC Converters for Tethered Mobile       |     |

|    |      | Machir  | ne Power Supply                                                    | 56  |

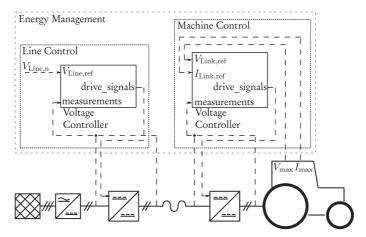

|    |      | 3.4.1.  | Electrical Architecture for a HVDC Tethering System for            |     |

|    |      |         | Mobile Machinery                                                   | 58  |

|    |      | 3.4.2.  | Power Management for a HVDC Tethering System for Mobile            |     |

|    |      |         | Machinery                                                          | 61  |

| 4. | Volt | age Cor | ntrol of LLC Converters                                            | 63  |

|    | 4.1. | Mather  | matical Model of a Modular DC / DC Converter                       | 64  |

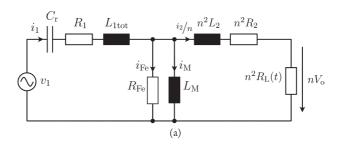

|    |      | 4.1.1.  | Electrical Equivalent Circuit for the Converter                    | 64  |

|    |      | 4.1.2.  | Branch and Junction Equations and State-Space Model For-           |     |

|    |      |         | mulation and Classification                                        | 65  |

|    |      | 4.1.3.  | Model Analysis                                                     | 69  |

|    | 4.2. | Contro  | ol Strategies for Converter Modules                                | 76  |

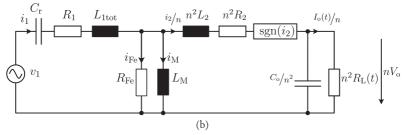

|    |      | 4.2.1.  | Startup Routine for Controlled Output DC Capacitor Charging        | 77  |

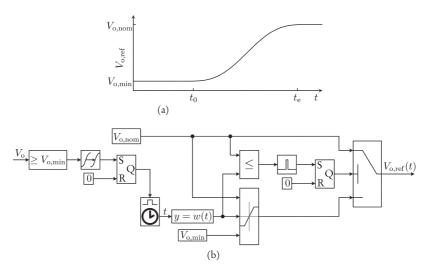

|    |      | 4.2.2.  | Conception of the Fundamental Controller Structure for the         |     |

|    |      |         | Converter Module                                                   | 80  |

|    |      | 4.2.3.  | Feed Forward Control                                               | 81  |

|    |      | 4.2.4.  | Feedback Control                                                   | 85  |

|    |      | 4.2.5.  | Signal Conditioning for the Combination of Feedback and            |     |

|    |      |         | Feedforward Control                                                | 86  |

|    |      | 4.2.6.  | Definition of a Benchmark Test for Dynamic Load Tests              | 86  |

|    | 4.3. |         | ol Algorithm for a Modular DC/DC Converter                         | 87  |

|    |      | 4.3.1.  | Individual Module Control for Modular DC/DC Converters             | 87  |

|    |      | 4.3.2.  | Global Control of Modular DC/DC Converters                         | 89  |

| 5. | Eval | uation  |                                                                    | 93  |

|    | 5.1. |         | rter Simulation Model Validation                                   | 94  |

|    | 5.2. |         | tive Evaluation of the Converter Control Concept                   | 97  |

|    |      | 5.2.1.  | Startup in Simulation                                              | 98  |

|    |      | 5.2.2.  | Single Module Converter Control                                    | 99  |

|    |      | 5.2.3.  |                                                                    | 101 |

|    |      | 5.2.4.  | Impact Analysis of Parameter Variances on the Converter            | 104 |

Contents

|     | 5.3.                                 | 5.3.1.<br>5.3.2.                                  | mental Test Results                                                                                                                                       | 114<br>117               |

|-----|--------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 6.  | Con                                  | clusion                                           | and Future Work                                                                                                                                           | 125                      |

|     | A.1.<br>A.2.<br>A.3.<br>A.4.<br>A.5. | Branch<br>Stabilit<br>Startup<br>Extend<br>Conver | Petails and Derivations and Junction Equations for a Converter Module by of Switched Linear Systems by Lyapunov's Direct Method . c Trajectory Generation | 131<br>135<br>136<br>139 |

|     | B.2.                                 | Prototy                                           | ype Design Documentation                                                                                                                                  | 142                      |

| Bil | oliogi                               | raphy                                             |                                                                                                                                                           | 147                      |

| Su  | pervi                                | sed The                                           | eses'                                                                                                                                                     | 155                      |

| Pu  | blicat                               | tions                                             |                                                                                                                                                           | 157                      |

| Cu  | ırricu                               | lum Vi                                            | tae                                                                                                                                                       | 159                      |

## List of Abbreviations

AC Alternating Current

ADC Analog to Digital Converter ASM Asynchronous Machine

CO<sub>2</sub> Carbon-Dioxide

CQLF Common Quadratic Lyapunov Function

DC Direct Current

EMI Electromagnetic Interference

EU European Union

FHA First Harmonic Approximation

HF High Frequency

HIL Hardware in the Loop

HV High Voltage

HVAC High-Voltage Alternating Current HVDC High-Voltage Direct Current

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistor

IT Isolé Terre

LHD Load Haul Dumper LTI Linear Time-Invariant

LV Low Voltage

LVAC Low-Voltage Alternating Current

MF Medium Frequency

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

MPC Model Predictive Control

MPPT Maximum Power Point Tracking

PCB Printed Circuit Boards

PFC Power Factor Correction

PID Proportional Integral Der

PID Proportional-Integral-Derivative

PRC Parallel Resonance Converter

PWM Pulse Width Modulation

RMS Root Mean Square

SISO Single Input Single Output

SPICE Simulation Program with Integrated Circuit Emphasis

SRC Series Resonance Converter

zcs Zero Current Switching

zvs Zero Voltage Switching

## List of Latin Symbols

| Symbol                                               | Description                                                  | Unit             |

|------------------------------------------------------|--------------------------------------------------------------|------------------|

| $\overline{A}$                                       | State matrix                                                 |                  |

| $oldsymbol{A}_{	ext{NN}}$                            | Zero dynamics system matrix                                  |                  |

| $\boldsymbol{A}_1$                                   | State matrix for positive secondary current                  |                  |

| $oldsymbol{A}_{-1} \ 	ilde{oldsymbol{A}}$            | State matrix for negative secondary current                  |                  |

| $	ilde{m{A}}$                                        | Preconditioned state matrix                                  |                  |

| $f_{\rm aw,min}$                                     | Anti-windup upper limit                                      | $_{\mathrm{Hz}}$ |

| $f_{\rm aw,max}$                                     | Anti-windup lower limit                                      | $_{\mathrm{Hz}}$ |

| $oldsymbol{A}_0$                                     | State matrix for zero secondary current                      |                  |

| b                                                    | Single-input state space input vector                        |                  |

| C                                                    | Capacitance                                                  | F                |

| $C_{\mathrm{GC}}$                                    | Miller capacitance: Gate to collector capacitance of an IGBT | $\mathbf{F}$     |

| $C_{\rm GE}$                                         | Gate to emitter capacitance of an IGBT                       | $\mathbf{F}$     |

| $c_{\mathrm{ies}}$                                   | Total capacitance in a gate circuit capacitance              | F                |

| $C_{\mathrm{in}}$                                    | Input blocking capacitor                                     | $\mathbf{F}$     |

| $C_{\mathrm{o}}$                                     | Output filtering capacitor                                   | $\mathbf{F}$     |

| $c_{ m os}$                                          | Parasitic output capacitance of a semiconductor element      | F                |

| $C_{ m r}$                                           | Resonance capacitance                                        | $\mathbf{F}$     |

| $C_{\mathrm{rp}}$                                    | Parallel resonance capacitance                               | $\mathbf{F}$     |

| $oldsymbol{c}^{C_{	ext{rs}}} oldsymbol{c}^{	ext{T}}$ | Series resonance capacitance                                 | $\mathbf{F}$     |

| $oldsymbol{c}^{	ext{T}}$                             | State space output matrix                                    |                  |

| D                                                    | Diode                                                        |                  |

| $\Delta f_{\mathrm{sw}}$                             | Inverter switching frequency range                           | Hz               |

| d                                                    | State space transparency                                     |                  |

| e                                                    | Control error                                                |                  |

| $e_{ m act}$                                         | Control error threshold for PID activation during startup    |                  |

| $f_{ m fb}$                                          | Feedback controller output frequency                         | $_{\mathrm{Hz}}$ |

| $f_{ m ff}$                                          | Feed forward controller output frequency                     | $_{\mathrm{Hz}}$ |

| $f_{ m sw,min}$                                      | Minimal switching frequency                                  | $_{\mathrm{Hz}}$ |

| $oldsymbol{f}_{	ext{sw,min}}$                        | Vector of minimal switching frequencies                      | Hz               |

| $f_{\rm sw,max}$                                     | Maximal switching frequency                                  | $_{\mathrm{Hz}}$ |

| Symbol                      | Description                                                        | Unit             |

|-----------------------------|--------------------------------------------------------------------|------------------|

| $f_{\rm n}$                 | Converter switching frequency, normalized versus the resonance     | 1                |

|                             | frequency                                                          |                  |

| $oldsymbol{F}_{\mathrm{n}}$ | Breakpoint matrix for the lookup table with normalized frequencies | 1                |

| $m{f}_{ m n}$               | Vector of equidistant, normalized frequencies                      | 1                |

| $f_{ m r}$                  | Resonance frequency                                                | $_{\mathrm{Hz}}$ |

| $f_{\mathrm{r}1}$           | Lower resonance frequency for resonance circuits with two          |                  |

|                             | resonance frequencies                                              | $_{\mathrm{Hz}}$ |

| $f_{ m sw}$                 | Inverter switching frequency                                       | $_{\mathrm{Hz}}$ |

| $i_1$                       | Transformer primary current                                        | Α                |

| $i_2$                       | Transformer secondary current                                      | Α                |

| $i_{ m C}$                  | Collector current                                                  | Α                |

| $I_{ m ds}$                 | Drain (so source) current                                          | Α                |

| $i_{ m d}$                  | Diode current                                                      | Α                |

| $i_{ m Fe}$                 | Transformer core lose equivalent current                           | Α                |

| $i_{ m M}$                  | Transformer magnetizing current                                    | Α                |

| $I_{ m max}$                | Upper current limit                                                | Α                |

| $I_{ m Link,ref}$           | Reference voltage for the electrical mobile machine's DC-link      | Α                |

| $I_{ m o}$                  | Converter DC output current RMS value                              | Α                |

| $i_{\rm o}$                 | Converter DC output current                                        | Α                |

| $i_{ m r}$                  | Converter resonance current                                        | Α                |

| $I_{ m RRM}$                | Reverse peak current                                               | Α                |

| $i_{ m sec}$                | AC secondary current of the converter / transformer                | Α                |

| $I_{\mathrm{tail}}$         | IGBT tail current                                                  | Α                |

| L                           | Inductance                                                         | Η                |

| $L_1$                       | Primary leakage inductance of a transformer                        | Η                |

| $L_2$                       | Secondary leakage inductance of a transformer                      | Η                |

| $L_{ m M}$                  | Transformer magnetizing inductance                                 | Η                |

| $L_{ m n}$                  | Normalized inductance in an LLC resonance converter                | Η                |

| $L_{ m r}$                  | Resonance inductance                                               | Η                |

| $L_{ m rp}$                 | Parallel resonance inductance                                      | Η                |

| $L_{ m rs}$                 | Serial resonance inductance                                        | Η                |

| $L_{1\mathrm{tot}}$         | Total primary side inductance inductance                           | Η                |

| $M_{ m DC}$                 | Stationary, normalized converter DC gain                           | 1                |

| $M_{ m fha}$                | Stationary converter gain of the FHA model                         | 1                |

| $M_{\rm fha,ext}$           | Stationary converter gain of the extended FHA model                | 1                |

| $m{M}_{ m fha,ext}$         | Matrix of stationary converter gain values of the extended FHA     |                  |

|                             | model                                                              | 1                |

| $m{m}_{ m fha,ext}$         | Vector of equidistant stationary converter gain values of the      |                  |

|                             | extended FHA model                                                 | 1                |

| Symbol                      | Description                                                         | Unit |

|-----------------------------|---------------------------------------------------------------------|------|

| $M_{\rm max}$               | Maximal design value for the stationary converter gain              | 1    |

| $M_{\min}$                  | Minimal design value for the stationary converter gain              | 1    |

| $M_{\rm ref}$               | Converter gain, required to achieve reference output voltage        | 1    |

| N                           | Total number of converter modules                                   |      |

| n                           | Transformer turns ratio                                             | 1    |

| $N_1$                       | Number of transformer primary turns                                 | 1    |

| $N_2$                       | Number of transformer secondary turns                               | 1    |

| P                           | Arbitrary positive definite symmetric matrix                        |      |

| p                           | Grade of the trajectory polynomial                                  |      |

| $P_{\text{Load}}$           | Converter load power                                                | W    |

| $P_{\text{Load,set}}$       | Converter load set-point                                            | W    |

| $P_{\text{nom}}$            | Nominal power                                                       | W    |

| $P_{\rm v}$                 | Power loss                                                          | W    |

| $P_{\mathrm{v,D}}$          | Power dissipation in a diode                                        | W    |

| $P_{\rm v,full}$            | Conducting power dissipation in a full bridge                       | W    |

| $P_{\rm v,half}$            | Conducting power dissipation in a half bridge                       | W    |

| $P_{ m v,Tfb}$              | Power dissipation in the converter secondary side with full bridge  | W    |

|                             | rectifier                                                           |      |

| $P_{ m v,Tct}$              | Power dissipation in the converter secondary side with center taped | W    |

|                             | transformer                                                         |      |

| Q                           | Arbitrary positive definite symmetric matrix                        |      |

| $Q_{\mathrm{e}}$            | Primary side equivalent quality factor of a loaded LLC converter    | 1    |

| $Q_{\mathrm{e}}$            | Quality factor of the FHA converter model                           | 1    |

| r                           | Relative grade of a dynamic system                                  |      |

| $R_1$                       | Resistance of the transformer primary side winding                  | Ω    |

| $R_2$                       | Resistance of the transformer secondary side winding                | Ω    |

| $R_{\mathrm{df}}$           | Diode forward conducting resistance                                 | Ω    |

| $R_{\rm e}$                 | AC side load equivalent resistance                                  | Ω    |

| $oldsymbol{r}_{ m e}$       | Vector of AC side load equivalent resistance                        | Ω    |

| $R_{\mathrm{Fe}}$           | Transformer core loss equivalent resistance                         | Ω    |

| $R_{\rm L}$                 | Load equivalent resistance                                          | Ω    |

| $R'_{ m L}$                 | Primary side transformed load equivalent resistance                 | Ω    |

| $R_{\rm on}$                | Semiconductor switch on-state resistance                            | Ω    |

| $R_{\text{on,full}}$        | Total $R_{\text{on}}$ in the current path of a full bridge          | Ω    |

| $R_{\text{on,half}}$        | Total $R_{\rm on}$ in the current path of a half bridge             | Ω    |

| S                           | (Semiconductor) switch                                              |      |

| $oldsymbol{S}_{\mathrm{B}}$ | Observability Matrix of a System                                    |      |

| $oldsymbol{S}_{\mathrm{S}}$ | Controllability Matrix of a System                                  |      |

| t                           | Time                                                                | S    |

| Symbol                  | Description                                                     | Unit |

|-------------------------|-----------------------------------------------------------------|------|

| $t_0$                   | Start time                                                      | s    |

| $T_1$                   | Transformer of the LLC resonance converter                      | 1    |

| $t_{ m d}$              | Dead time between the on states of an inverter                  | S    |

| $t_{ m e}$              | End time instance of a transition                               | S    |

| $t_{ m fade}$           | Voltage fade out time                                           | S    |

| $t_{ m fi}$             | Current fall time                                               | S    |

| $t_{ m fv}$             | Voltage fall time                                               | S    |

| $t_{ m on/off}$         | Turn-on respectively turn-off time                              | S    |

| $t_{ m ri}$             | Current rise time                                               | S    |

| $t_{ m rv}$             | Voltage rise time                                               | S    |

| $T_{\rm s}$             | Simulation / computation step size / Sampling time              | S    |

| $T_{\rm s,C}$           | Sampling time of the control algorithm                          | S    |

| $T_{ m s,M}$            | Sampling time of the converter's simulation model               | S    |

| $T_{ m s,R}$            | Sampling time of the simulation data recording                  | S    |

| $T_{\rm sw}$            | Converter switching period at operating frequency $f_{\rm sw}$  | s    |

| $t_{ m tail}$           | Current tail time                                               | s    |

| u                       | SISO state space system input – Control value                   |      |

| $V(\boldsymbol{x})$     | Lyapunov function                                               |      |

| $v_1$                   | Input voltage of the converter's resonance network              | V    |

| $v_2$                   | Transformer secondary voltage                                   | V    |

| $v_{\rm CE}$            | Collector-Emitter voltage                                       | V    |

| $V_{\rm CEon}$          | Collector-Emitter on state saturation voltage                   | V    |

| $v_{\rm Cr}$            | Resonance capacitor voltage                                     | V    |

| $\hat{v}_{\mathrm{Cr}}$ | Resonance capacitor peak voltage                                | V    |

| $V_{ m dc}$             | DC voltage                                                      | V    |

| $V_{ m df}$             | Diode forward voltage                                           | V    |

| $V_{ m dr}$             | Diode reverse blocking voltage                                  | V    |

| $v_{\mathrm{DS}}$       | Drain-Source voltage                                            | V    |

| f                       | Vector field, general expression for a state function           |      |

| $V_{\mathrm{E},k}$      | Electric base potential of the $k^{\text{th}}$ converter module | V    |

| $V_{ m f}$              | Fundamental of the converter input square wave voltage          | V    |

| $v_{\mathrm{Fe}}$       | Voltage across the magnetizing core equivalent resistor         | V    |

| $V_{ m FRM}$            | Turn-on voltage peak of the diode                               | V    |

| $v_{\mathrm{GS}}$       | Gate-Source voltage                                             | V    |

| $V_{ m in,min}$         | Minimal DC input voltage for the DC/DC converter                | V    |

| $V_{ m in}$             | Input voltage of an electrical network                          | V    |

| $V_{\rm in,nom}$        | Nominal DC input voltage for the DC/DC converter                | V    |

| $V_{ m Line,n}$         | Nominal tethering line voltage                                  | V    |

| $V_{ m Line,ref}$       | Reference voltage for the tethering line controller             | V    |

| Symbol                      | Description                                                   | Unit |

|-----------------------------|---------------------------------------------------------------|------|

| $v_{ m M}$                  | Transformer magnetizing voltage                               | V    |

| $V_{\rm max}$               | Upper voltage limit                                           | V    |

| $V_{\mathrm{Mod}}$          | Terminal voltage of a converter module                        | V    |

| $V_{\rm Link,ref}$          | Reference voltage for the electrical mobile machine's DC-link | V    |

| $V_{\rm o}$                 | Output voltage of an electrical network                       | V    |

| $V_{\text{oe}}$             | Primary side transformed converter load RMS voltage           | V    |

| $V_{ m o,inf}$              | Finite value of a stabile output voltage                      | V    |

| $V_{ m o,min}$              | Minimally achievable output voltage of the DC/DC converter    | V    |

| $V_{ m on}$                 | Device on state voltage drop                                  | V    |

| $V_{ m o,nom}$              | Nominal output voltage of the DC/DC converter                 | V    |

| $V_{ m o,ref}$              | Output voltage reference value                                | V    |

| $V_{ m r,in}$               | Input voltage of a resonance circuit                          | V    |

| $V_{\rm r,o}$               | Output voltage of a resonance circuit                         | V    |

| $\bar{w}_{\mathrm{e}}$      | End value of a trajectory for a system transition             |      |

| $\bar{w}_0$                 | Start value of a trajectory for a system transition           |      |

| $W_{ m on/off}$             | Turn-on respectively turn-off energy dissipation              | J    |

| w                           | Reference trajectory for an output transition                 |      |

| $oldsymbol{x}_{\mathrm{e}}$ | Equilibrium Point of a system                                 |      |

| $oldsymbol{x}_{	ext{N}}$    | Zero dynamics states                                          |      |

| $\boldsymbol{x}$            | System states vector                                          |      |

| y                           | Output variable in a state SISO state space system            |      |

## List of Greek Symbols

| Symbol                     | Description                                  | Unit |

|----------------------------|----------------------------------------------|------|

| δ                          | Number of any non-infinite size              |      |

| $\Delta M_{ m G}$          | Operative range of gain of a DC/DC converter | 1    |

| $\Delta P_{\mathrm{Load}}$ | Defined converter load range                 | W    |

| $\Delta V_{ m p}$          | Voltage overshot                             | V    |

| $\epsilon$                 | Arbitrarily low number of any non-zero value |      |

| $\sigma$                   | State matrix switching parameter             |      |

## 1. Introduction

Electrical power transmission and conversion experiences a continuously increasing relevance in academia and industry due to constantly growing demand of electrical energy in nearly every aspect of life. Additionally, efforts to reduce Carbon-Dioxide (CO<sub>2</sub>) emissions and other environmental protective aspects, result in constantly tightening emission regulations for a vast number of applications throughout the world. In the electrical energy generation sector, this leads to a changing situation due to decentralization by a growing share of renewable energy sources. Additionally, electrification of further applications, e.g., from the transportation sector and mobile machinery, adds to the growing demand for electric energy and the increased research interest. Regarding mobile machinery, as of the year 2010, in the European Union (EU) non-road mobile machinery contributed 2 % of the Unions total CO<sub>2</sub> emission [VVHFF10].

Decentralization of the electrical energy generation and increased energy demand lead to more dynamics in the electric energy transmission paths and transmitted power in the energy transmission grid. The dynamics are induced due to the higher volatility of the renewables: if one renewable energy source produces high excess supply in one region, this will be transmitted to a region, where the demand exceeds the current generation capacity. While the transmission amount and direction are subject to a highly dynamic process in such a system, the energy transmission paths in a classical supply grid are not static but still far less dynamical. Second, the energy supply of systems as electrified vehicles of all kind or mobile machines display additional loads of significant measure, which further stresses the grid. In response, transmission technology and energy conversion techniques are under research with respect to meet these changing requirements.

The following sections will briefly set the topics of electrical energy transmission and electrical energy conversion in the context of its current utilization. Transmission and conversion techniques and their applications are sketched out and chances, offered by Modular High Voltage (HV) DC/DC Converters are motivated. This introduction closes with an outline of this theses.

2 1. Introduction

## 1.1. Electrical Energy Transmission

In a classical grid, electrical energy is transmitted from the electrical power plant to the consumer via a High-Voltage Alternating Current (HVAC) grid. At the power plant site, the voltage is transformed to HV with a transformer, fed into the grid, transmitted to the consumers region, where it is transformed back to Low Voltage (LV) and fed to the LV distribution grid. This method is known as HVAC transmission, voltages up to 400 kV are commonly used in Europe. Transformation to and from HVAC with transformers is a long known, relatively cheap technique. Losses on the transmission line are considerably low, but due to the capacitive nature of the transmission loss with increasing distance. This fact limits the economically reasonable maximal transmission voltage and distance. In literature, HVAC transmission is considered economically reasonable for distances up to a few hundred km [KSW13, Ch. 7.2], [OO11, Ch 19.5].

To connect, for example power plants in remote areas or offshore wind farms to the electric grid, HVAC transmission quickly reaches its practicable limits, due to the above discussed loss to distance relation. In such cases, High-Voltage Direct Current (HVDC) transmission is applied, where the source power is transformed, rectified and fed to the transmission line in Direct Current (DC) form. The DC transmission line represents a point-to-point connection. On its end the current is inverted back to Alternating Current (AC), transformed and fed to the HVAC grid. Within HVDC transmission, no reactive losses exist and hence, voltages up to some MV are possible. Since the majority of the cost and the losses occur in the head stations and HVAC is reasonably cheap on short distances, HVDC transmission is mainly applied for distances above 1000 km, where it is more economical than HVAC and for sea cables – where the parasitic capacitance per meter is large – above 40 km [Sch12, Ch. 10]. With the rising growth of the renewable energy generation sector and the corresponding increasing distance between power source and sink, HVDC transmission becomes more and more interesting for academia and industry.

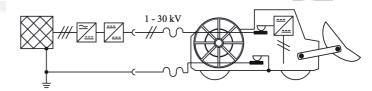

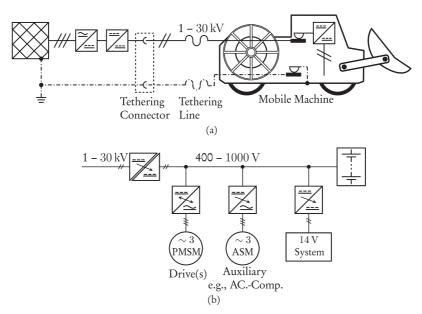

Besides the energy sector, a second application, where high electric power has to be transmitted is that of tethered mobile machines, namely in the open pit and underground mining industry [YFM09, JHB14]. In the state-of-the-art setup, these machines, like large excavators and LHDs, have a reel installed on the body, whereon a tethering line is stored. The schematical setup of the power supply of such a tethered mobile machine is given in Figure 1.1. On the operating site, a 50 Hz or 60 Hz three-phase transformer isolates the site's energy supply net versus earth potential, forming an Isolé Terre (IT)-net. The machine is connected to the site's net via a reelable,

Figure 1.1.: Schematics of the power supply of a tethered machine on the example of an electrical underground mining Load Haul Dumper (LHD).

flexible tethering line, which is stored on a reel on the LHD. From the reel, the energy is transmitted to the machines electric drives via a set of slip rings. The drives – here depicted in the form of an Asynchronous Machine (ASM) – usually power hydraulic pumps for the bucked operation, moving power, etc.. The power is transmitted in AC machine voltage level, which requires thick and heavy tethering lines, even for low power. The machine's action radius arises from the available tethering line on the reel. For current machines with Low-Voltage Alternating Current (LVAC) supply, this is limited to a few hundred meters due to the thick LV lines [JHB14]. To increase the power, that can be installed on such a machine and/or the possible operating radius without reconnecting the tethering line to another connection point, the transmission systems power density must be increased. Therefore, the most promising option is increasing the transmission voltage. Increasing the power density could possibly be an enabler to apply tethering systems to more mobile machines – also in further industries.

## 1.2. Electrical Energy Conversion

Electrical energy converters are widely used in many different applications, like electric power generation and transmission, electric motor applications and the voltage supply of many end devices. Converters for AC to AC (transformer / frequency converter), DC to DC (DC/DC converter), AC to DC (rectifier) and vice versa (inverter) exist. The converter power ratings reach from few mW up to the multi-MW range. Especially in high power applications, conversions between different voltage levels are often implemented with a transformer to obtain a more stable design and in some application

4 1. Introduction

cases to isolate the different grids from each other. In some applications it is necessary to operate transformers in higher frequency to safe installation space and weight. For simple rectification, diode rectifiers can be utilized, however for higher conversion power, rectifiers with active Power Factor Correction (PFC) technologies are used to reduce Electromagnetic Interference (EMI) emissions (e.g., distortion reactive power) to the AC grid. In (two phase) inverters, electronic switches like Metal-Oxide-Semiconductor Field Effect Transistors (MOSFET) or Insulated Gate Bipolar Transistors (IGBT) are arranged and driven in a way, such that the positive DC voltage is alternately conducted to the two conductors of the (AC) output – it is the inverse operation of a rectification.

In recent years, some trends with positive influence on research efforts in power converter technology can be observed. One is the increasing use of renewable energy and the therewith ongoing growth of the market for HVDC transmission, where high-voltage and high-power power converters are required [HBM+13, MP15]. Second the growing interest in electrification in the automotive industry and for mobile machinery pushes the inverter and DC/DC converter technology [PTB10, SEMR+15, SJB15]. Major research goals are increased efficiency, reliability and power density [DBK12, LL10, MLC+08]. To keep stress of the grid by harmonic distortion and reactive power low, the improvement of the waveform quality for grid connected converters becomes more relevant with increasing number and power rating and hence, is subject to research and must comply with legal regulations and valid standards e.g., *EN 50160:2010 Voltage characteristics of electricity supplied by public distribution networks* [CEN10], [Ank00, Ch. 10].

To meet these given development objectives, one major focus lies in the improvement of the physical characteristics of the converter components. Ohmic losses are reduced and fast switching capabilities are increased. For high-voltage applications, efforts to increase the maximal blocking voltage of semiconductor switches are undertaken. The current limit for commercially available IGBTs lies at 6.6 kV, in research, blocking voltages as high as 13 kV are reported [CRC+09]. For a few years, on the circuit side, resonance switching techniques are state-of-the-art in commercially available power converters. In such converters, resonance circuits are excited in the vicinity of their characteristic frequency, generating a waveform that allows the semiconductor switches to be turned on and off close to the zero-crossing instance of the oscillation. This technique leads to quasi-lossless operation with significantly reduced stress to the semiconductor components and EMI emissions. This loss and stress reduction enables more efficient, faster converter operation and can increase its robustness. Higher frequencies reduce the size and weight of passive components, so that higher volumetric and gravitational power densities can be achieved. With smaller passive

components, usually the cost can also be reduced, contrary, fast switching capable semiconductors might counteract the economical goal.

For power conversion at the endpoints of HVDC transmission lines, converters with a structure, that is known as multilevel converter is presented in literature and is commercially available. The key in these converters is the division of the terminal voltage to series connected power semiconductor switches. By the voltage division, voltages, that are higher than the blocking voltage of a single semiconductor switch can be handled. This splitting of the voltage to the semiconductors can be achieved for example with diodes (e.g., diode clamped converter) ore capacitors (flying capacitor, modular multilevel converter). For example, a brief review on existing multilevel inverter topologies is given e.g., in [Mün11].

A further field of application, where high voltage is divided over a number of semiconductor switches are electrical railway traction systems, it is also described in [SR07, MLC+08]. From the catenary wire, a number of full bridge rectifiers are connected in series at their AC terminals, each rectifier output feeds into a separate low voltage DC link. From there, DC/DC converters with magnetic coupling generate the voltage for the drive systems. Here the magnetic coupling ensures that the voltage drop across the input semiconductors is leveled out.[MLC+08] For high power DC/DC applications, a patent [Rei02] describes a setup, where the DC capacitors of DC/DC converters form a capacitive voltage divider. The voltage dividers outer terminal is connected to the high voltage output terminal.

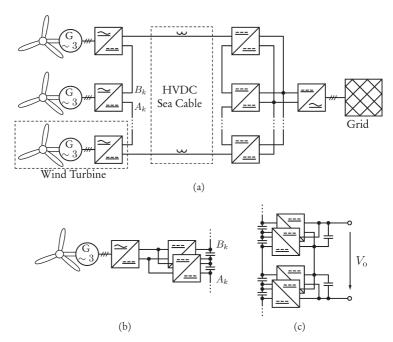

For the connection of high-power offshore wind farms to the HVDC line, new distributed converter concepts based on DC/DC converters are discussed in academia for a few years already, e.g., in [HJSK11, MP15]. In the given references, it is proposed to series connect the DC output of the single wind turbines and thereby form the high DC voltage for transmission to shore. This way, the complexity of the single wind turbines increases, but the need for a central conversion station is obsolete.

Even though the described systems greatly differ from each other, they all have in common, that a voltage, that is too high to be switched by one semiconductor switch, is distributed over a number of semiconductors and that high frequency is applied for voltage conversion.

## 1.3. Motivation and Objectives of this Publication

With this publication, the concepts from literature regarding high voltage power converters with modular structure is picked up and brought into a form, where it is suitable to be installed on a tethered mobile machine. The goal is to show, that with a DC/DC converter with a compact design, a mobile machine can be tethered by

6 1. Introduction

HVDC. This way, the total tethering systems power density is increased and either more tethering line or more machine power can be installed on the machine. Both are key factors to spread tethered machinery technology to further industry sectors. With the chosen approach, the high tethering line voltage is distributed between a number of converter modules. The then small maximal voltage on one module (semiconductor switch) allows the utilization of semiconductors with fast switching capabilities. In combination with state-of-the-art resonance switching technologies, high power densities can be achieved and high power ratings are implementable on the very limited space of a mobile machine.

The publication is outlined as follows. In the following Section 2, the state-of-theart of resonant switched DC/DC converters are outlined, an in-detail view for LLC converters is given, control methods for DC/DC converters are briefly discussed and the theory on linear switched systems is summed up. Section 3 justifies the converter architecture and closes with example applications, once, for an offshore wind farm power conversion and second the implementation of a HVDC tethering system on a mobile machine. Mathematical system analysis and controller design on module and system level are located in Section 4. In Section 5, results from simulation and measurements from a scaled prototype are given. The publication is closed with a conclusion of the work and an outlook to new perspectives in Section 6.

## 2. State-of-the-Art of Resonant Switched DC / DC Power Converters

The input inverter of conventional switched mode DC/DC converters is driven by Pulse Width Modulation (PWM) in hard switching mode. With the hard switching technique, the semiconductor switches are forcefully turned on, while the full rated voltage is applied to them and forcefully turned off, while the full rated current runs through them. Output voltage and current are rated by variation of the inverter duty cycle and therewith by the voltage-time-integral. This operating scheme allows compact converter designs with good efficiency, mayor losses occur during switching of inductive loads in the switched semiconductors. Contrary, hard switching operation of semiconductor switches in circuits with inductive components induces stress by voltage and current peaks during turn-off and -on, respectively. These peaks and sharp edges during switching results in high EMI [MUR03, Ch. 9] [Lut12, Ch. 6].

In the following chapter, methods to further improve the converter operating characteristics are discuses and a survey over the state-of-the-art of these techniques, namely zero voltage / zero current switching, is given. In the second part of this chapter, resonant DC/DC converter topologies with one, two and three resonant elements are given and state-of-the-art modeling and design methods are discussed. For the converter operation, an overview over control strategies from literature for DC/DC converters in general and resonant converters in particular are given. If not otherwise specified, in the following content, it will be taken as given, that IGBTs are utilized for power semiconductor switches in the converters.

## 2.1. Zero Voltage / Zero Current Switching

The goal in soft switching is to turn on the semiconductor switch under zero voltage condition, where the voltage drop across the switch is neglectable, and turn it off under

zero current condition, when no or little current flows through the semiconductor. The concept of Zero Current Switching (zcs) in power converter circuits reaches back to the early 1970s [Sch70], the one of Zero Voltage Switching (zvs) back to the late years of the same decade [KSY79]. Towards hard switching operation, these techniques aim improvements in a number of physical effects, as power dissipation and EMI.

#### 2.1.1. Switching behavior and losses in IGBTs

The thermal energy, lost in the current carrying path during a turn-on or -off transition of an IGBT is given by

$$W_{\text{on/off}} = \int_{t_0}^{t_{\text{on/off}}} \left( v_{\text{CE}}(t) i_{\text{C}}(t) \right) dt, \tag{2.1}$$

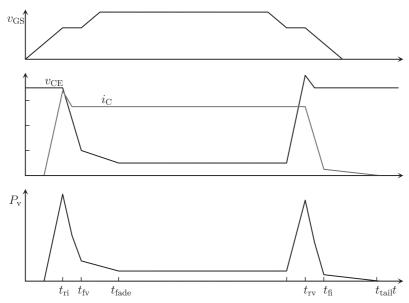

where  $W_{\rm on/off}$  is the lost energy during turn-on or -off, respectively.  $v_{\rm CE}$  is the collector to emitter voltage and  $i_{\rm C}$  is the collector current of the IGBT. The respective transition for turn-on or -off starts at time  $t_0$  and ends at  $t_{\rm on/off}$ . The typical voltage and current waveforms during hard switching turn-on and -off transitions are visualized in the middle diagram of Figure 2.1, the top diagram shows the corresponding IGBT Gate-to-Source voltage  $v_{\rm GS}$  and in the lower diagram, the power dissipated in the semiconductor's channel is given. The individual sections and their physical correlations are well described in literature like [MUR03, Ch. 25] and [Lut12, Ch. 3]. From the waveform in the figure, it can be observed, that during turn-on, the current rises, before the voltage starts falling to its on-value  $V_{\rm CEon}$  during the conducting phase and during turn-off, the voltage rises to the blocking voltage before the current begins to fall. This results in the power dissipation peaks, displayed in the figure during turn-on and -off.

For an IGBT in a circuit with inductive load, according to [Lut12] and the piecewise integration of the turn-on time interval from Figure 2.1 according to equation (2.1), the dissipated turn-on energy per pulse resolves to

$$W_{\rm on} = \frac{1}{2} V_{\rm dc} (i_{\rm C} + I_{\rm RRM}) t_{\rm ri} + \frac{1}{2} V_{\rm dc} (i_{\rm C} + \frac{2}{3} I_{\rm RRM}) t_{\rm fv} + \frac{1}{2} V_{\rm CEon} t_{\rm fade}, \tag{2.2}$$

where  $V_{

m dc}$  is the DC voltage applied to the circuit,  $I_{

m RRM}$  is the reverse peak current of the freewheeling diode and  $V_{

m CEon}$  is the on voltage drop of the channel. The time intervals are  $t_{

m ri}$  for the current rise time,  $t_{

m fv}$  for the voltage fall time and  $t_{

m fade}$  for the voltage fading to  $V_{

m CEon}$ . [Lut12] The first two summands correspond to the fact that the device current rises before the voltage starts falling, these two contribute

Figure 2.1.: Typical simplified voltage and current waveforms and corresponding power dissipation of an IGBT

the majority of the total turn-on losses in hard switching condition. The height of the peak current  $I_{\rm RRM}$  is proportional to the current rise  $^{\rm d}i/_{\rm d}t$  and the strength of  $i_{\rm C}$  in conducting mode, which leads to additional stress to the IGBT and high EMI radiation. Respective to the turn-on losses, the integral for the turn-off loss yields

$$W_{\text{off}} = \frac{1}{2} V_{\text{dc}} i_{\text{C}} t_{\text{rv}} + \frac{1}{2} (V_{\text{dc}} + \Delta V_{\text{p}}) i_{\text{C}} t_{\text{fi}} + \frac{1}{2} I_{\text{tail}} V_{\text{dc}} t_{\text{tail}}, \tag{2.3}$$

with the voltage peak  $\Delta V_{\rm p}$  and the tail current  $I_{\rm tail}$ . The time intervals correspond to the voltage rise time  $t_{\rm rv}$ , the current fall time  $t_{\rm fi}$  and the tail current time  $t_{\rm tail}$ . [Lut12] Corresponding to the turn-on losses, the first two summands contribute the majority to the hard switching energy loss, however the loss, caused by the tail current is larger than the one caused by the voltage fading. The voltage overshoot is proportional to the current  $i_{\rm C}$  and the voltage rise factor  ${\rm d}v/{\rm d}t$  roots in the inductances of the current path.

On the gate side of a MOSFET or an IGBT, the loss roots from the repetitive charging and discharging of the input capacitance  $c_{\text{ies}} = C_{\text{GE}} + C_{\text{GC}}$ . The gate

| ching methods [ w 1 11(13, p. 273]   |                             |                   |  |

|--------------------------------------|-----------------------------|-------------------|--|

| Semiconductor                        | Maximal Operating Frequency |                   |  |

| Switch Type                          | Hard Switching              | Soft Switching    |  |

| MOSFET                               | $100\mathrm{kHz}$           | $250\mathrm{kHz}$ |  |

| $1200\mathrm{V}	ext{-}\mathrm{IGBT}$ | $20\mathrm{kHz}$            | $150\mathrm{kHz}$ |  |

| 1700 V-IGBT                          | $10\mathrm{kHz}$            | $150\mathrm{kHz}$ |  |

Table 2.1.: Operating frequency limits of semiconductor switches for hard- and soft switching methods [WNTR15, p. 275]

charge current repetitively flows through the gate resistor and through the upper and lower driver transistor, while charging and discharging respectively and by this emits charging losses. [WNTR15]

To reduce the switching losses, the area under the power curve in Figure 2.1 must be reduced. In hard switching operation, this would mean, that the rise- and fall times of voltage and current in the switching instance must be reduced to reduce switching losses. The time intervals  $t_{\rm ri}$  and  $t_{\rm fv}$  at turn-on as well as  $t_{\rm rv}$  and  $t_{\rm fi}$  at turn-off are approximately proportional to the IGBT gate resistance and can be reduced, to a certain degree, by the use of a lower gate resistance. [Lut12, WNTR15] The time intervals  $t_{\rm fade}$  and  $t_{\rm tail}$  cannot be influenced. A reduction of these discussed time intervals, would reduce the results of equations (2.2, 2.3) and hence the switching losses. While the goal of reducing losses is reached in the switches, the losses in the reverse diodes are increased [WNTR15]. The voltage overshot

$$\Delta V_{\rm p} = L_{\rm par} \frac{\mathrm{d}i_{\rm C}}{\mathrm{d}t} + V_{\rm FRM},\tag{2.4}$$

is proportional to the steepness of the current falling slop  $^{\mathrm{d}ic}/_{\mathrm{d}t}$  and the turn-on voltage peak of the diode  $V_{\mathrm{FRM}}$  and hence, will be increased by reducing the switching time. The increase of the overshot and the steeper current and voltage slopes generate stronger undesirable EMI and component stress [Ank00, p. 321]. Hence, increasing the switching transient time does not lead to improved overall switching behavior.

The discussed effects of hard switching on efficiency, EMI and component stress are the major motivations to develop methods, where the collector-emitter voltage drops preferably to zero, before the collector current starts rising during the turn-on transition and vice versa, the current drops to zero, before the voltage rise starts at turn-off. Further, with reduced switching losses per transition, the operating frequency of power electronic circuits can be increased without increasing the overall thermal

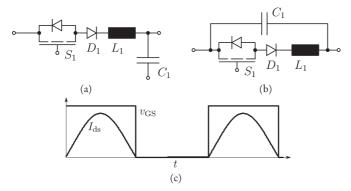

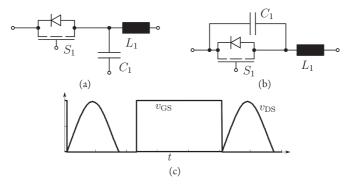

Figure 2.2.: L-type (a) and M-type (b) zero current switch in accordance to [LL84]. Subfigure (c) displays the switch control voltage and switch current of a buck converter with zero current M-type switch.

stress on the switched semiconductors. As a consequence, increased frequencies lead to smaller passive components and hence more compact and often more cost-efficient converter designs. Table 2.1 recites an overview of switching boundaries for hard- and soft switching frequencies for a selection of power semiconductor switches, especially IGBTs profit from soft switching operation by increased operation frequencies. [MUR03, p. 251] [WNTR15, p. 273] Soft switching is gained by the zcs and zvs, the transient behavior of both is discussed in the following sections.

### 2.1.2. Zero Current Switching

An early description of zcs was published in 1970 by Schwarz [Sch70]. In his publication a Series Resonance Converter (SRC) with a thyristor half bridge inverter is presented, where an LC series resonant circuit in the primary side, forms an appropriate current wave form to turn on the thyristors under zero current condition. In the following decade, Liu et al. presented two types of zero current switches and experimentally demonstrated its functionality with MOSFETs [LL84]. The schematics of the L- and M-type switching networks, presented by Liu et al., are given by Subfigure 2.2a and 2.2b, respectively. The circuits consist of a semiconductor switch  $S_1$ , an inductance  $L_1$  and a capacitor  $C_1$ . If the switch has a free-wheeling diode – like in the Figure – a serial diode  $D_1$ , reversely polarized to the free-wheeling diode must be installed to block the reverse current path through the freewheeling diode. The current  $I_{ds}$  of a zero current MOSFET switch with its gate voltage  $v_{GS}$  is plotted in

Subfigure 2.2c. When the switch is turned on, the current describes a quasi-sinusoidal half-wave form, there is no instantaneous current rise, the switch is turned on at zero current. While conducting, the current rises to its maximum and drops back to zero, where the switch is turned off under zero current condition. For further details on L-and M-type zero current switches refer to [LL84]. With the described circuits, zcs is possible and the  $\frac{\mathrm{d}i}{\mathrm{d}t}$  is reduced in the switching network, but the voltage waveform still contains sharp edges, hence, EMI issues are reduced, but still remain.

The internal dynamics of an IGBT, turned off under zero current condition was investigated by Trivedi et al. in [TS99]: When an IGBT is turned off at zero current, a large amount of excess charge remains inside the semiconductor, at hard turn-off, this charge forms the IGBT-specific tail current. During the following time, this remaining charge decays partly by recombination and mainly by equal electron and hole currents inside the semiconductor. When the external voltage rises high enough, the remaining charge is swept out. Due to the minor remaining charge at the instance of the voltage rise time, this part of the turn-off losses is lower than the hard switching turn-off loss part of the tail current in equal system configuration but non-zero.

### 2.1.3. Zero Voltage Switching

To achieve zero voltage switching in practice, the current is commutated to the antiparallel diode of the semiconductor switch. Then, the voltage drop across the switch is equal to the voltage drop of the conducting diode - which is near zero - and the switch is turned on. After the current is reversed, it commutates from the diode to the already fully conducting channel. Two switching networks for zvs are presented in [LL90], that are similar to the zcs switch from section 2.1.2. The half-wave mode switches, given in the reference, are shown in Subfigure 2.3a and 2.3b respectively. Refer to the reference for the full-wave setup of these switching circuits. In both switching networks, one terminal of the capacitor is connected between the semiconductor and the inductance. The capacitor, that is connected directly to the switch terminals, shapes an appropriate voltage waveform to turn on the semiconductor at zero voltage, as displayed for the example of a MOSFET switch in part (c) of the figure. In the instance of turn-off of the MOSFET, its drainsource voltage  $v_{\rm DS}$  is zero. After the zero-voltage turn-off,  $v_{\rm DS}$  starts to describe a quasi-sinusoidal wave form, rises to its maximum and falls back to zero before the end of the off-time of the device. At the end of the off-time,  $v_{\rm DS}$  is still zero and the MOSFET can be turned on under zero voltage condition. Liu et al. also state, that the junction capacitances are already discharged at switching time, which further reduces the switching losses in the channel. [LL90]

Figure 2.3.: Half-wave mode L-type (a) and M-type (b) switches for zero voltage switching according to [LL90] Subfigure (c): Switch control voltage and switch voltage drop of a zero voltage M-type switch in a boost converter.

At zero voltage turn-off of IGBTs, the remaining charge in the device causes a current bump with following tailing current. At the same time, the emitter-collector voltage starts to rise and power is dissipated. Compared to zcs, the distinct existence of current tails leads to higher losses in zvs-circuits with IGBTs. Contrary, circuit design is simpler and component values are smaller for zvs designs. [TS99] Zvs turn-on and quasi-zcs turn-off for IGBT was experimentally evaluated by Pavlovsky et al. [PdHF06]. Concordant to the effects, described in [TS99], the lowest turn-off loss was measured in devices with very small tail currents.

#### 2.2. Resonant Switched Converters

The zero current and zero voltage switches described in the forgoing sections can be used for zcs / zvs in buck- and boost-type converters with one single switch (see [LL84, LL90]). For converter types with half- or full bridge inverter and rectifiers, it appears more suitable to approach this subject more comprehensively. However, the insights from the previous sections still hold their significance: To enable zvs and / or zcs, an appropriate waveform must be formed, ideally, for zvs the voltage, and for zcs the current, should be close to sinusoidal. To achieve these wave forms, a resonance circuit – also known as resonance tank – is formed with one, two or three energy storage elements e.g., capacitors and inductors. Due to their specific switching circuits, these converter types are also known as resonant switched converters or resonance converter.

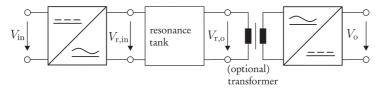

Figure 2.4.: Structure of a resonance DC/DC converter with input inverter, resonance tank, optional transformer and output rectifier

Resonance converter topologies can be classified by different characteristics. The most common classifications are the arrangement of their energy storage elements, e.g., series-, parallel connected [Yan03, p. 95 – 106], and by the number of their storage elements, respectively their number of resonance peaks [Bat94].

The common structure of a resonance converter is given in Figure 2.4. The DC input voltage Vin is inverted by a half- or full bridge inverter. The resonance tank, consisting of two, three or four energy storage elements, is excited by the resonance tank input voltage  $V_{r,in}$ , which is the output of the inverter. The converter may have an optional transformer to adept the converters output voltage to a desired voltage range. If a transformer exists, the resonance tank output voltage is applied to it, else, it is fed to the rectifier. The rectified and filtered converter output is the DC voltage  $V_0$ . For the following discussions, it appears handy to focus on the analog filter characteristic of the resonance circuit to describe its effect on the converter voltage gain at varying inverter switching frequency. The damping behavior of this filter is influenced by the converter load, incoherently off the resonance tank topology, higher loads affect stronger damping behavior. Hence, the output voltage of a certain resonance tank depends on the switching frequency and the converter load. Typically, the output voltage regulation is accomplished by the variation of the switching frequency. The voltage gain characteristics of resonant converters are typically visualized by their steady state voltage gain characteristics, where the ratio between the resonance tank input and the output voltage is drawn over the operation frequency at various loads.

In the next subsections, resonance converter topologies will be classified by the number of their resonance peaks, and topologies with one, two and three resonance peaks will be introduced and briefly discussed. In topologies with more than one resonance frequency,  $f_{\rm r}$  always denotes the resonance frequency at full load. Following, a more detailed insight into the LLC converter topology will be given. A comprehensive survey over resonance tank layouts with two, three and four storage elements is given in [Bat94].

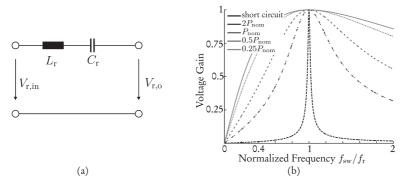

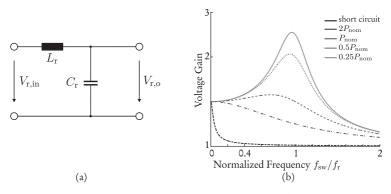

Figure 2.5.: Resonance tank (a) and voltage gain diagram (b) of a LC series converter

#### 2.2.1. Single Resonance Circuits

The energy storage elements in a single resonance circuit can be arranged, for instance, in series with the resonance tank output. This layout is known as Series-loaded or SRC [MUR03, Ch. 9]. A series resonance tank, formed of a capacitor  $C_{\rm r}$  and an inductor  $L_{\rm r}$  is depicted in Figure 2.5a. The converter voltage gain is defined as the ratio between the resonance tank input- and output voltage,  $V_{\rm r,in}$  and  $V_{\rm r,o}$ , respectively and is commonly plotted over the normalized frequency  $f_{\rm sw}/f_{\rm r}$ . The associated voltage gain diagram for steady state operation at different loads over the switching frequencies is given in part (b) of the Figure. For simplicity, the resistive power loss in the resonance circuit is commonly neglected. [MUR03, Yan03]

The resonance tank acts as an analog filter with variable resistive load, which can be mathematically described in the Laplace domain by the voltage gain function

$$G(s) = \frac{s}{\frac{L_r}{R_L} s^2 + s + \frac{1}{R_L C_r}},$$

(2.5)

where  $R_{\rm L}$  represents the converter load. It can be seen in the equation, that the resonance circuit is a second order bandpass filter with the eigenfrequency  $f_{\rm r}=1/2\pi\sqrt{L_{\rm r}C_{\rm r}}$ . By variation of the inverter switching frequency, the impedance of the filter varies and reaches its minimum at its eigenfrequency. The voltage gain diagram in Figure 2.5b shows the dependency between increasing load and decreasing damping behavior, further, it can be seen, that the gain never exceeds 1. The gain curves for all loads show rising slopes for switching frequencies below and falling slope above resonance. At resonance frequency, the gain is 1 for all load cases, which is the highest gain for

Figure 2.6.: Resonance tank (a) and voltage gain diagram (b) of a LC parallel converter.

SRCs. The described relations between load, frequency and damping can also be approached by physical interpretation. At resonance, the impedance of the filter is zero and all voltage drops at the load. Above and below resonance, the load voltage is proportionally divided to the impedance of the filter elements and the converter load. At switching frequencies below resonance, the phase of the filter is positive allows zcs. While the switching frequency approaches the gain peak, the phase decreases to zero, above the peak, at falling slope, the phase is negative and zcs is achieved.

If the output is utilized parallel to the capacitor of a second order resonance tank with an inductor in series with a capacitor, it is commonly known as Parallel Resonance Converter (PRC) [Ank00, Yan03]. The corresponding resonance tank layout and voltage gain curves are given in Figure 2.6. The voltage gain function in the Laplace domain is

$$G(s) = \frac{1}{L_r C_r s^2 + R_L L_r s + 1}.$$

(2.6)

From the schematic in part (a) of the Figure and the gain function, it is obvious, that the resonance tank is a second order low pass. The gain curves for light load, which is equal to low damping, show rising slops and gain amplification towards the eigenfrequency. For increasing load, respectively damping,  $C_{\rm r}$  is more and more bypassed by the load. Hence, the peaks shift towards smaller frequencies, the achievable amplification decreases and at short circuit condition only falling slopes appear. Like in the SRC, rising slopes correspond to zvs and falling to zcs.

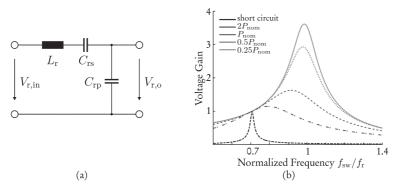

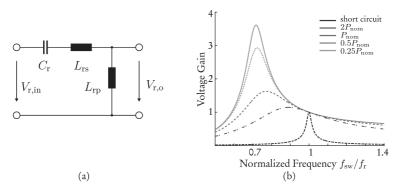

Figure 2.7.: Resonance tank (a) and voltage gain diagram (b) of a LCC series parallel converter

#### 2.2.2. Dual Resonance Circuits

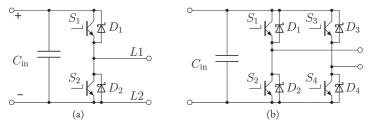

With a third energy storage element added to the system, resonance circuits with two gain peaks can be implemented. One type of three-element converters are series-parallel resonance converters, that add a second eigenfrequency to the network. Two series parallel resonance converters, the LCC and the LLC converter will be discussed in this section. An overview over resonance tank circuits with tree energy storage elements is given in [Bat94].

The LCC network is shown in Figure 2.7 and consists of a series inductance  $L_{\rm r}$ , a series capacitor  $C_{\rm rs}$  and a parallel capacitor  $C_{\rm rp}$ . The voltage gain function is visualized in part (b) of the figure, and the corresponding equation is

$$G(s) = \frac{s}{L_{\rm r}C_{\rm rp}s^3 + \frac{L_{\rm r}}{R_{\rm I}}s^2 + \left(\frac{C_{\rm rp}}{C_{\rm rs}} + 1\right)s + \frac{1}{R_{\rm I}C_{\rm rs}}}.$$

(2.7)

The network forms a third order bandpass with two eigenfrequencies. At high power the parallel capacitor is shortened by the load and hence, resonance occurs at  $f_{\rm r1}=1/2\pi\sqrt{L_{\rm r}C_{\rm rs}}$ . Like in the SRC, at this point the gain for all load cases is 1. With decreasing load, the influence of the parallel capacitance increases, which causes the resonance to shift to higher frequencies towards  $f_{\rm r}=1/2\pi\sqrt{L_{\rm r}\frac{C_{\rm rs}C_{\rm rp}}{C_{\rm rs}+C_{\rm rp}}}$  and – similar to the parallel resonance converter – the height of the gain maximum to increase. In zvs operation, LCC converters are problematic, due to their light load peaks in the frequency range between the zvs high load area and the zvs light load area. If the

Figure 2.8.: Resonance tank (a) and voltage gain diagram (b) of a LLC series parallel converter

converter load is reduced, the voltage peaks must be overcome to stabilize the output frequency, this can lead to damage on the converter [Yan03].

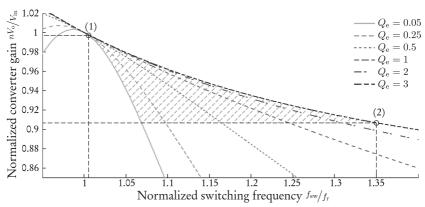

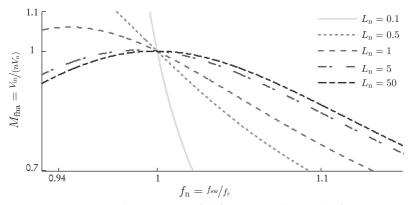

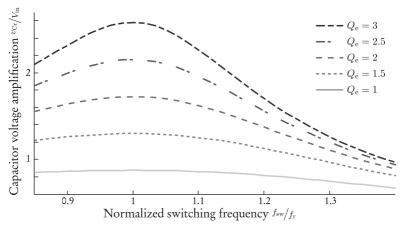

A second common way to form a series parallel resonance tank is to connect a capacitor  $C_{\rm r}$  and an inductor  $L_{\rm rs}$  in series and a second inductance  $L_{\rm rp}$  parallel to the load. This LLC topology and its voltage gain curves are depicted in Figure 2.8. The gain function is

$$G(s) = \frac{s^2}{\frac{L_{rs}}{R_L}s^3 + (\frac{L_{rs}}{L_{rp}} + 1)s^2 + \frac{1}{R_LC_r}s + \frac{1}{L_{rp}C_r}}.$$

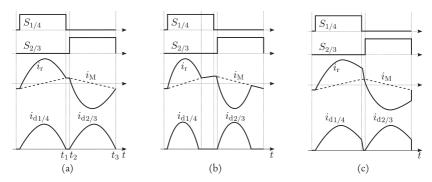

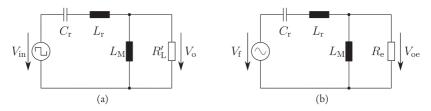

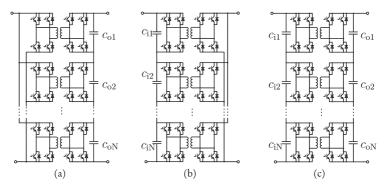

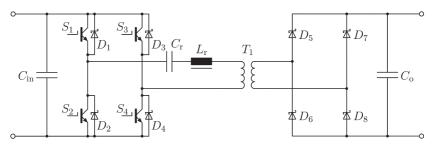

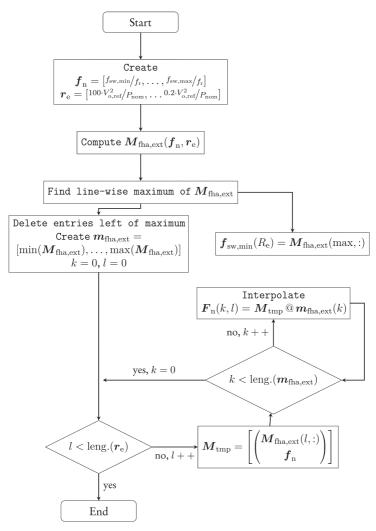

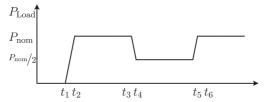

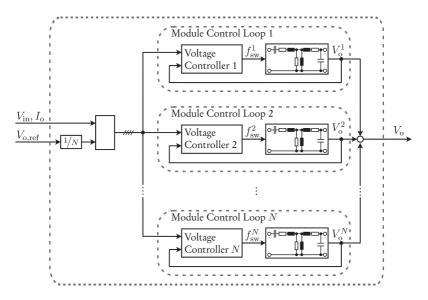

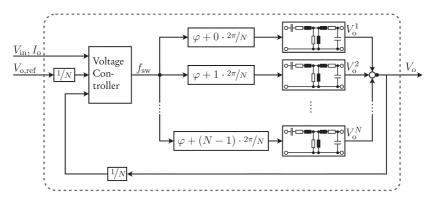

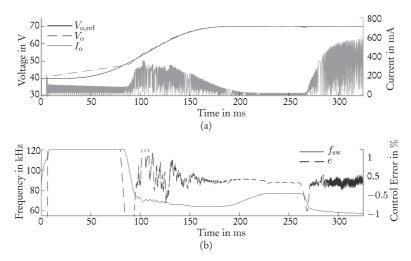

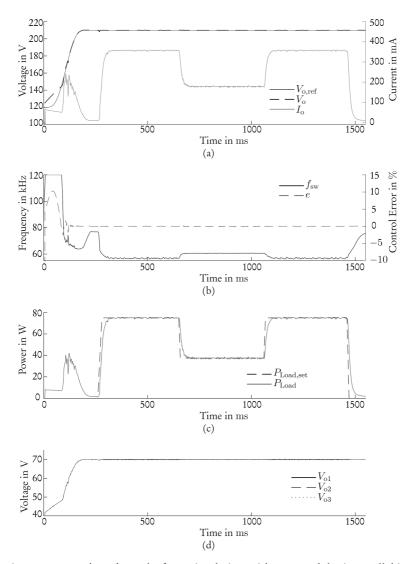

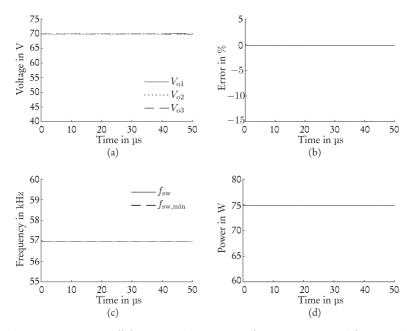

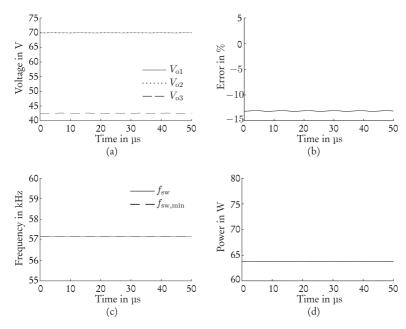

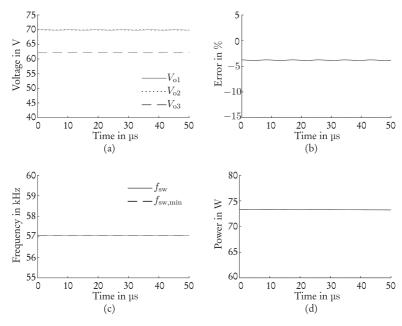

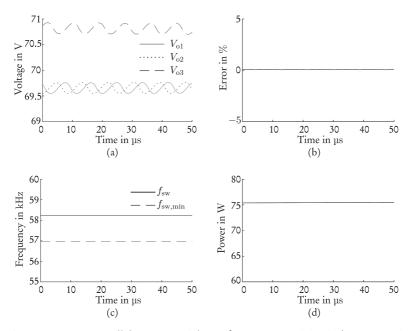

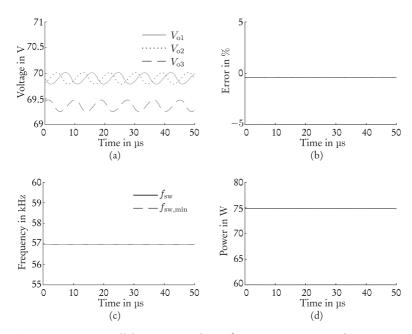

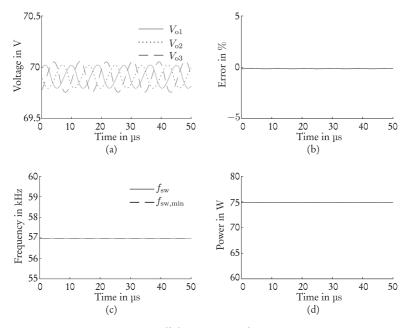

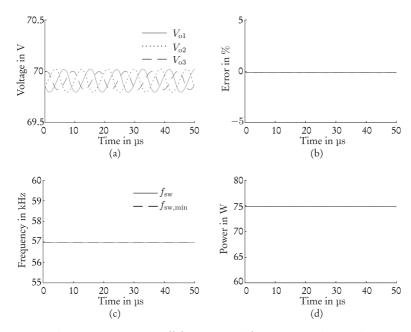

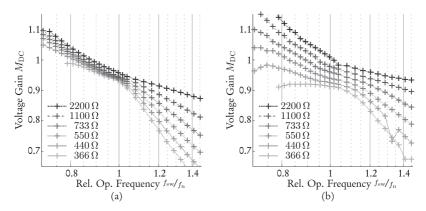

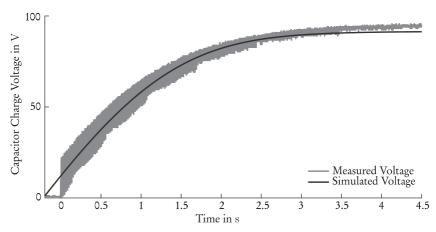

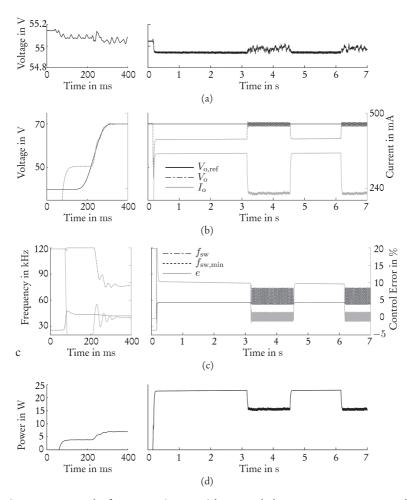

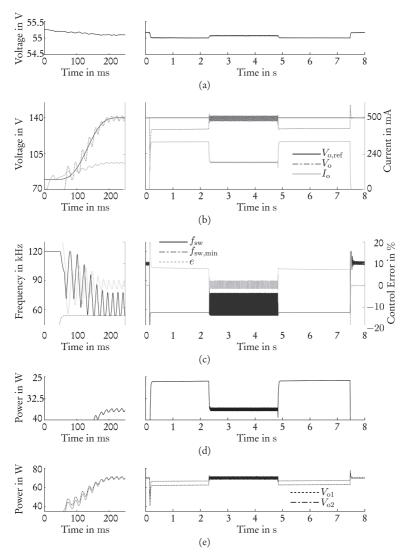

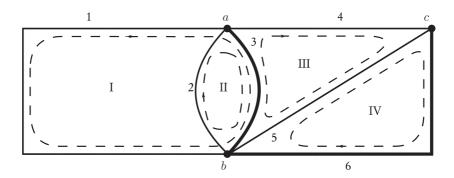

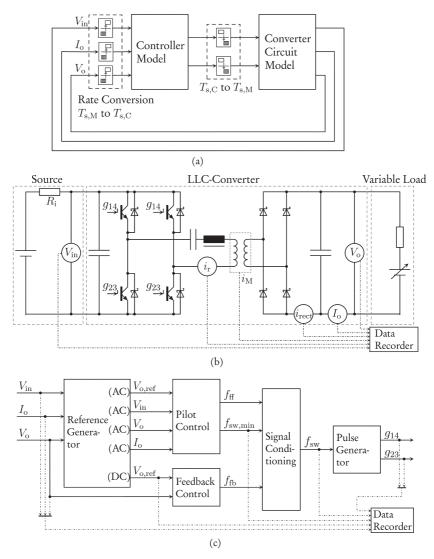

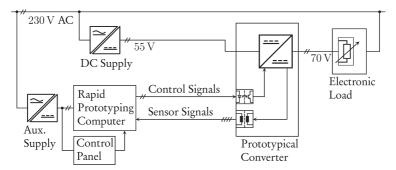

(2.8)